VHDL Startprojekt: LED mit Taster ansteuern

(EN google-translate)

(PL google-translate)

Nach Start von VIVADO:

|

1. Neues Projekt erstellen

"Create Project" anwählen:

Bild 0-1: "Create Project" anwählen.

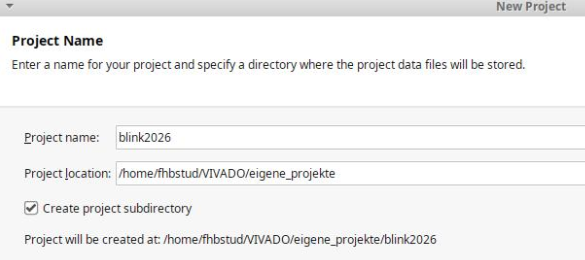

2. Projektname und Pfad festlegen

...Eventuell zuerst einen Ordner für eigene Projekte erstellen.

Bild 0-2: Projektname und Pfad festlegen.

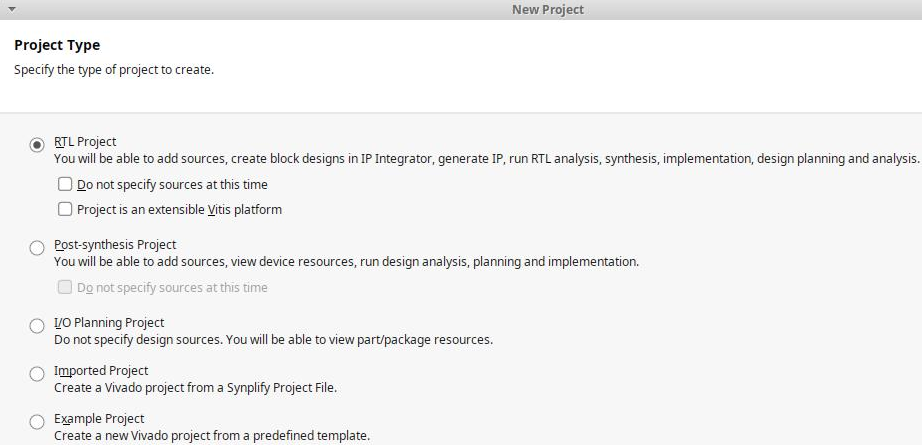

3. Projekttyp festlegen: RTL

Bild 0-3: Projekttyp festlegen: RTL

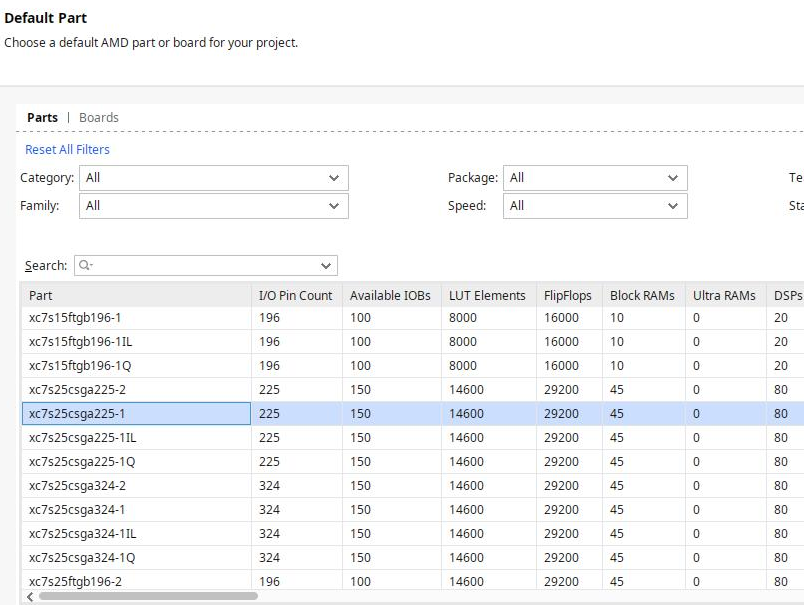

4. Den richtigen FPGA als Zielbaustein festlegen, hier Xilinx Spartan-7 FPGA (XC7S25-1CSGA225C)

Bild 0-4: Zielbaustein festlegen, hier Xilinx Spartan-7 FPGA (XC7S25-1CSGA225C)

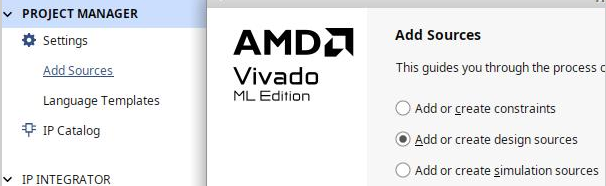

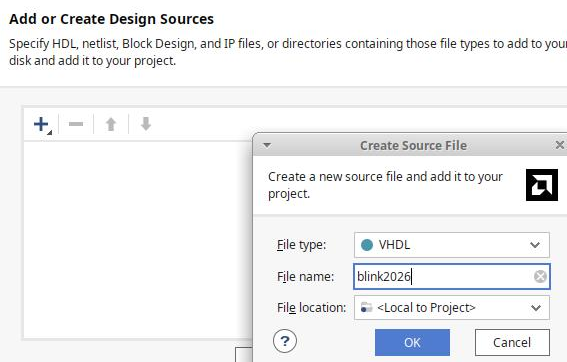

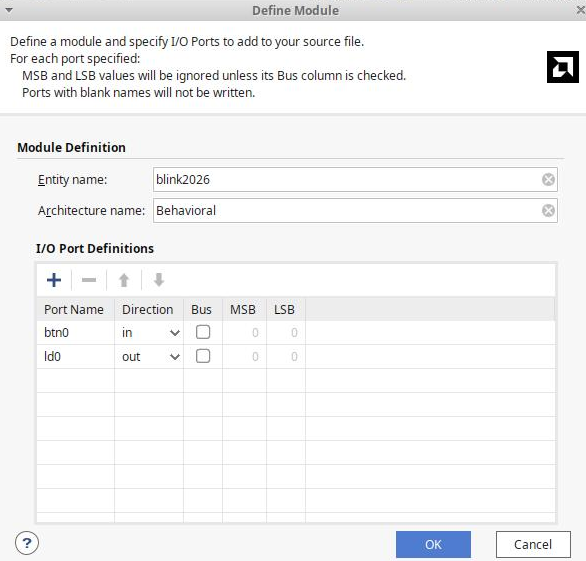

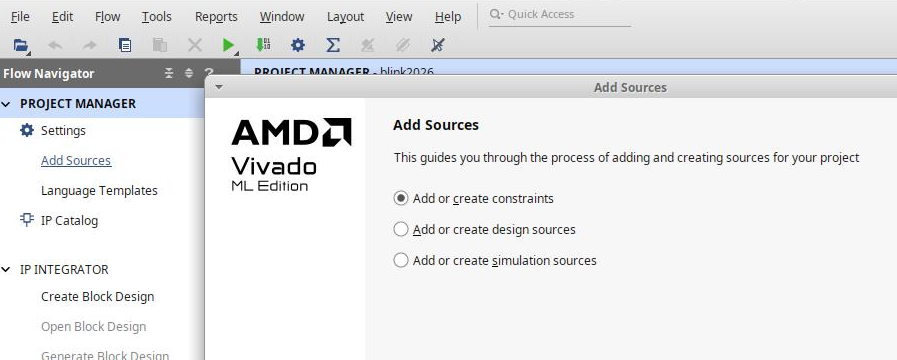

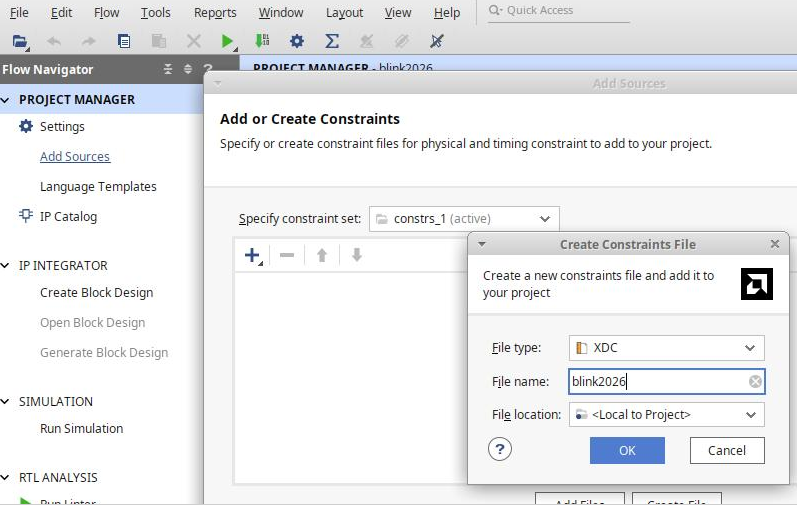

5. VHDL-Quelltextfile und Constraints-File erzeugen

Bild 0-5: VHDL-Quelltextfile und Constraints-File erzeugen.

Bild 0-6: VHDL-Quelltextfile und Constraints-File erzeugen.

Bild 0-7: VHDL-Quelltextfile und Constraints-File erzeugen -- Ein- und Ausgänge festlegen.

Bild 0-8: VHDL-Quelltextfile und Constraints-File erzeugen -- Constraints-Datei erzeugen.

Bild 0-9: VHDL-Quelltextfile und Constraints-File erzeugen -- Constraints-Datei erzeugen (Fortsetzung).

6. Einfügen der Quelltexte für das Beispiel:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx leaf cells in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity blink2026 is

Port ( btn0 : in STD_LOGIC;

ld0 : out STD_LOGIC);

end blink2026;

architecture Behavioral of blink2026 is

begin

ld0 <= btn0;

end Behavioral;

Code 0-1: blink2026.vhd, VHDL-Code.

# Buttons

set_property -dict { PACKAGE_PIN D2 IOSTANDARD LVCMOS33 } [get_ports { btn0 }]; #IO_L15N_T2_DQS_34 Sch=btn[0]

# LEDs

set_property -dict { PACKAGE_PIN J1 IOSTANDARD LVCMOS33 } [get_ports { ld0 }]; #IO_L8N_T1_34 Sch=led[0]

Code 0-2: blink2026.xdc, Constraints-Code, gewonnen aus Cmod-S7-25-Master.xdc.

7. Code-Synthese durchführen und Bitfile erstellen

Add sources finish => Aufforderung für Behavioural öffnet automatisch run synthesis run implementation ... wird vorgeschlagen open implemented design ... wird vorgeschlagen

Code 0-3: Ablauf Synthese von oben nach unten.

8. Verbindung zu FPGA herstellen und Programm NICHT PERSISTENT übertragen

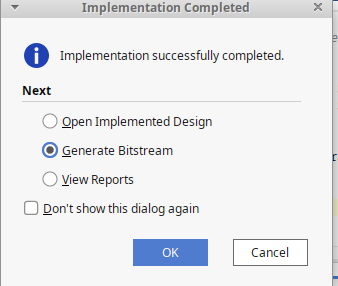

Bild 0-10: Bitstream Datei erzeugen.

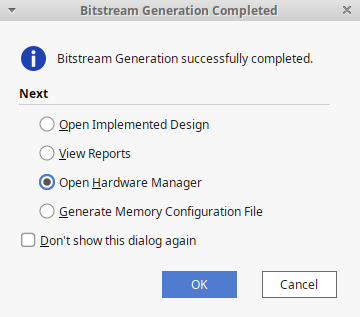

Bild 0-11: Open Hardware Manager -- NICHT Open implemented Design.

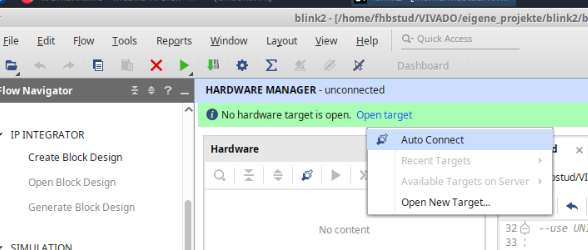

Bild 0-12: Verbinden mit Board.

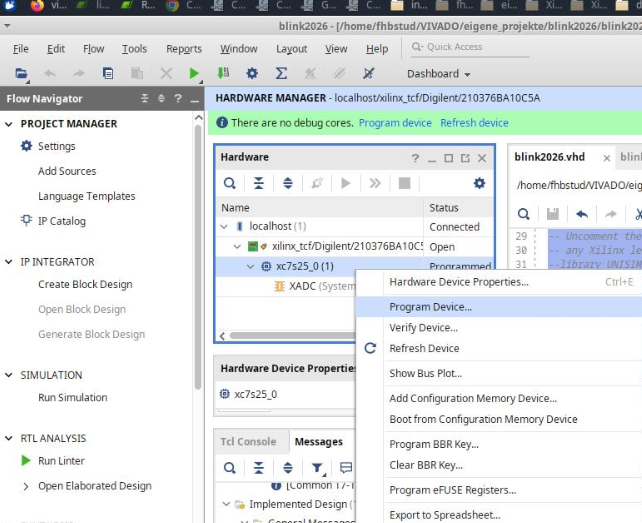

Auto Connect wählen, dann Program Device wählen:

Bild 0-13: Program Device wählen.

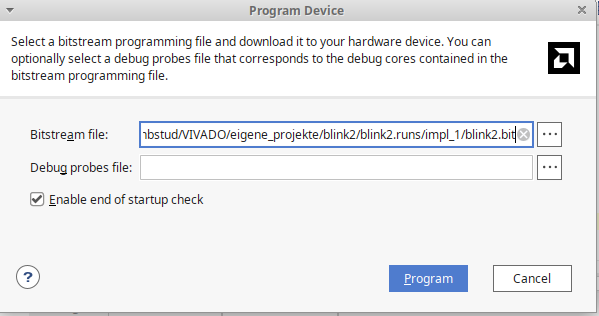

Bild 0-14: Bitstream übertragen.

9. Programm PERSISTENT übertragen

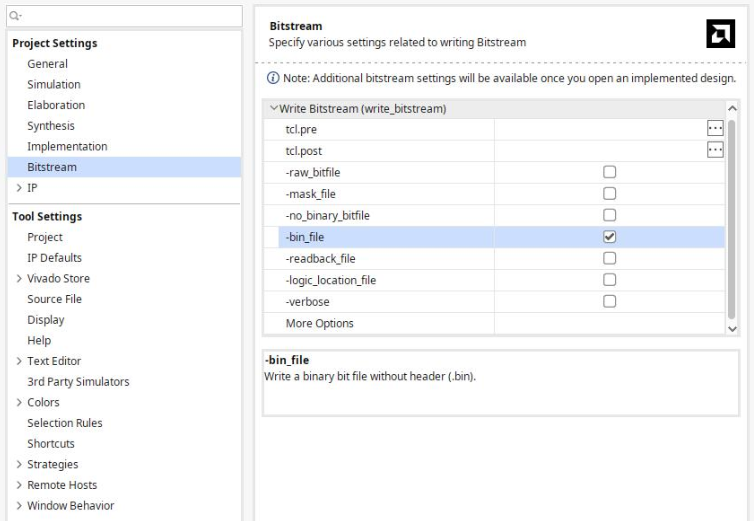

Bild 0-15: Bitfile übertragen auswählen.

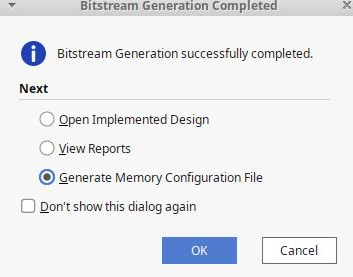

Bild 0-16: Memory Configuration File erzeugen lassen.

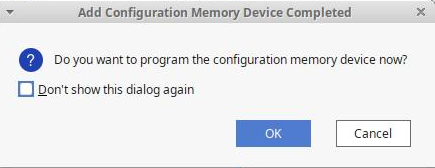

Bild 0-17: ...und übertragen.

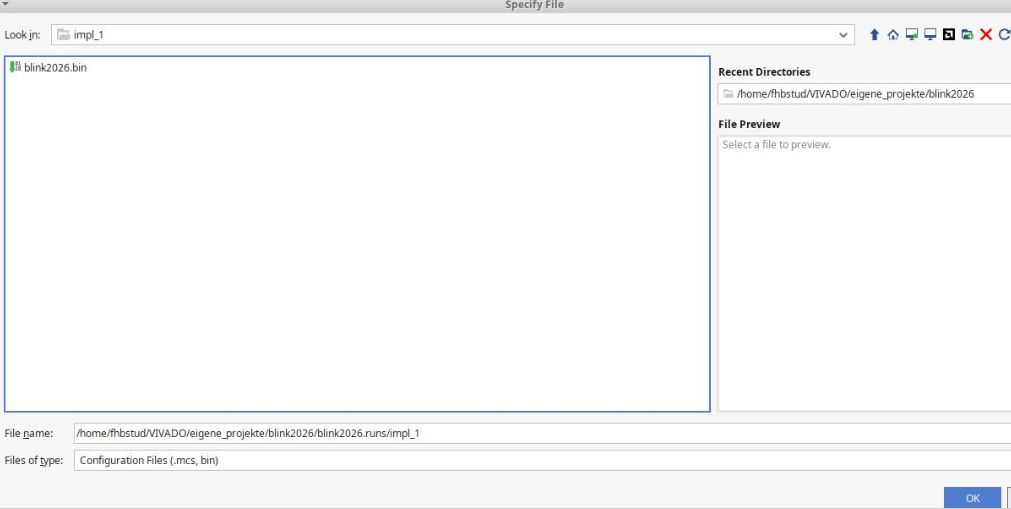

Bild 0-18: ....bin-File auswählen.

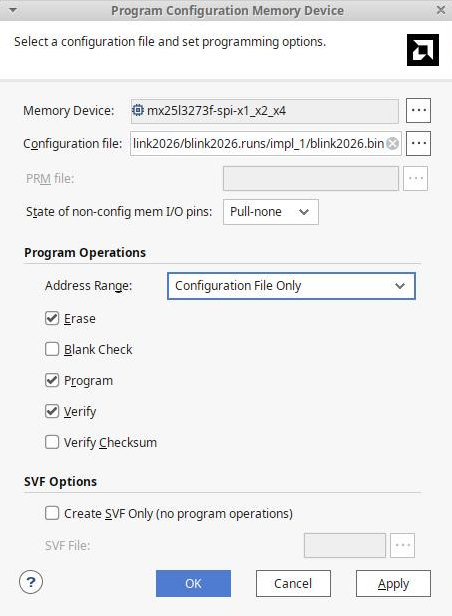

Bild 0-19: Konfiguration wählen.