DLP-FPGA

(EN google-translate)

(PL google-translate)

Datenblätter

Übersicht

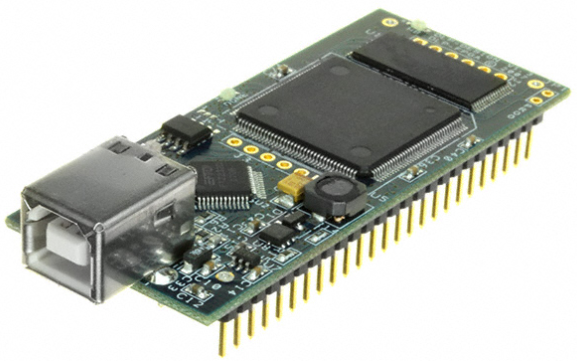

Bild 0-1: FPGA Evaluationsboard der Firma DLP.

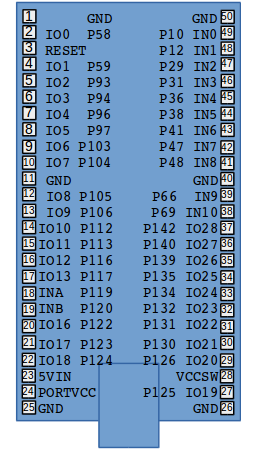

Bild 0-2: Zuordnung zwischen den Board-Pins und den FPGA-Chip-Pins (Xilinx Spartan 3E). Die Nummer der FPGA-Chip-Pins wird in den Programmen benötigt.

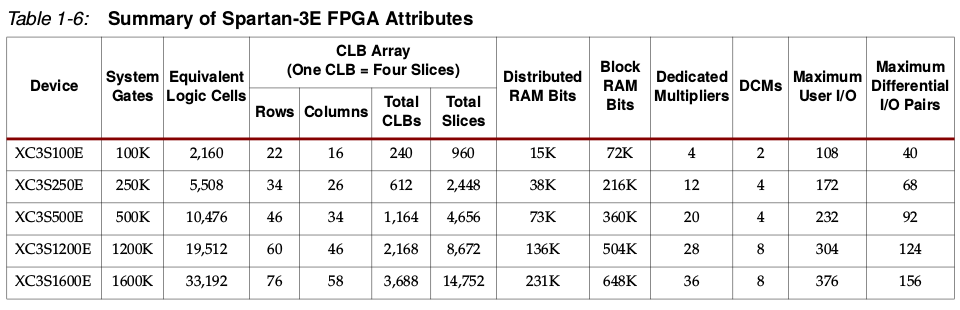

Bild 0-3: Spezifische Daten der Spartan 3A Familie von Xilinx. Der DLP-FPGA hat einen XCS250E verbaut, Quelle: Datenblatt FPGA ug331.pdf.

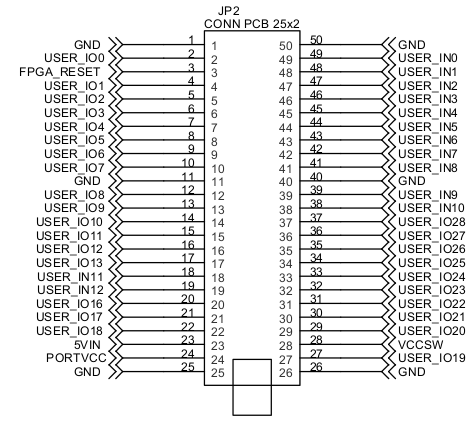

Bild 0-4: Zuordnung der herausgeführten Anschlüsse, Quelle: Datenblatt DLP-FPGA dlp-fpga-ds-v15.pdf.

Bild 0-5: Zuordnung der Anschlüsse des FPGA-Chips 1.

Bild 0-6: Zuordnung der Anschlüsse des FPGA-Chips 2.

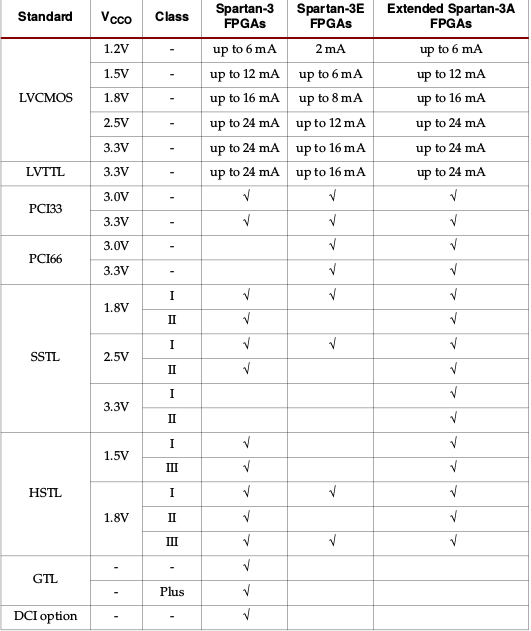

Bild 0-7: Elektrische Eigenschaften bei unterschiedlichen Pin-Konfigurationen, Quelle: Datenblatt FPGA ug331.pdf.

Die UNISIM-Bibliothek von Xilinx

Am Beginn der Lehrveranstaltung werden alle benötigten Komponenten mit Hilfe elementarer VHDL-Befehle erstellt.

Im weiteren Verlauf werden dann Primitive, wie Flip-Flops, Multiplexer und Schieberegister auch aus der UNISIM-Bibliothek genommen.

Hinweise hierzu:

Ein Manual zu den verfügbaren UNISIM-Elementen mit Hinweisen zu deren Instanziierung in VHDL für den Spartan 3E: