Getting Started - Entwicklung einer ersten Anwendung

(EN google-translate)

(PL google-translate)

Das nachfolgendes Beispiel ist angelehnt an ein einführendes Tutorial mit Xilinx ISE 13 von Lothar Miller:

Zusammenfassung

Es soll eine blinkende LED realisiert werden.

Als Ausgang für die LED wird einer der verfügbaren digitalen Ausgänge verwendet:

Bezeichnung auf DLP-FPGA-Board: USER_IO19 Pin-Nummer auf DLP-FPGA-Board: 27 Pin-Nummer auf FPGA-Spartan-Chip: 125 Bezeichnung auf FPGA-Spartan-Chip: IO_L05P_0/GCLK6

Code 0-1: Verwendeter digitaler Ausgang.

Als Clock für den zyklischen Vorgang werden die 6MHz verwendet, die ein Taktgeber von außen auf den FPGA-Spartan-Chip gibt. Die Flankenwechsel von diesem Eingang können im Programm abgerufen werden. Sie müssen dann noch entsprechend geteilt werden, um einen sichtbaren Blinkvorgang zu realisieren. Es wurde eine Vorteilung von 3000000 für einen Pegelwechsel gewählt. So erhält man ein Blinken von 1Hz.

Bezeichnung auf DLP-FPGA-Board: nicht herausgeführt Pin-Nummer auf DLP-FPGA-Board: nicht herausgeführt Pin-Nummer auf FPGA-Spartan-Chip: 56 Bezeichnung auf FPGA-Spartan-Chip: IP_L06P_2 / RDWR_B / G CLK0

Code 0-2: Verwendeter digitaler Clock-Eingang mit 6MHz.

Damit das Board mit Strom versorgt ist und die LED laufen kann, ist eine Möglichkeit, die 5-Volt der USB-Verbingung vom PC mit zu nutzen. Hierzu müssen auf dem die Pins 23 "5VIn" und Pin 24 "PORTVCC" zusammengeschaltet werden.

Projekt einrichten

Beim Anlegen eines neuen Projektes mit ISE wird zunächst abgefragt, welches Device verwendet wird. Hier ist es ein Spartan 3E, Typ XC3S250E, Geschwindigkeitsstufe 4, Bauform TQ144.

Kodierung

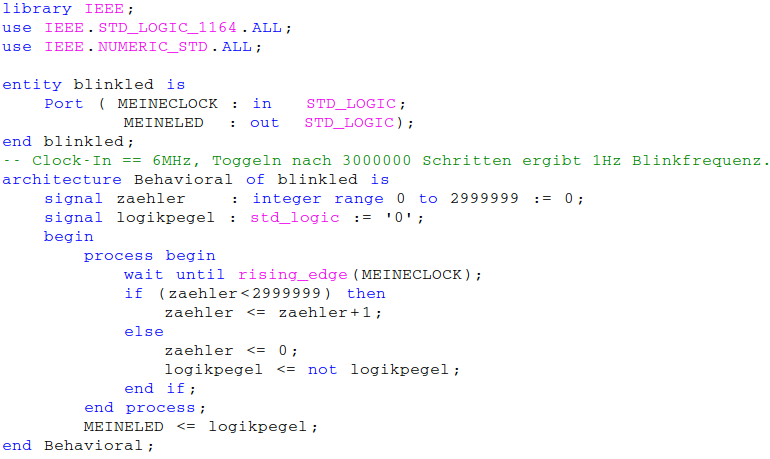

Nur die beiden nachfolgenden Dateien werden vom Programmierer erstellt. Alle anderen Dateien werden hieraus von der Entwicklungsumgebung ISE automatisch generiert.

Die Datei blinkled.vhd repräsentiert die Beschreibung der Schaltung, die automatisch generiert werden soll.

Die ihr beigeordnete Datei blinkled.ucf beschreibt, welchen physikalischen Pins des verwendeten Chips den in blinkled.vhd auftauchenden Ein- und Ausgängen zugeordnet werden sollen.

|

Die drei Generierungsschritte werden dadurch angestoßen, dass man im Fenster links oben von ISE diese doppelklickt, bzw. mit der rechten Maustasten anwählt und run startet. Sie heißen:

|

Bild 0-1: Generierungsschritte.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity blinkled is

Port ( MEINECLOCK : in STD_LOGIC;

MEINELED : out STD_LOGIC);

end blinkled;

-- Clock-In == 6MHz, Toggeln nach 3000000 Schritten ergibt 1Hz Blinkfrequenz.

architecture Behavioral of blinkled is

signal zaehler : integer range 0 to 2999999 := 0;

signal logikpegel : std_logic := '0';

begin

process begin

wait until rising_edge(MEINECLOCK);

if (zaehler<2999999) then

zaehler <= zaehler+1;

else

zaehler <= 0;

logikpegel <= not logikpegel;

end if;

end process;

MEINELED <= logikpegel;

end Behavioral;

Code 0-3: VHDL-Quelltext in Datei blinkled.vhd

## GCLK6 ist auf FPGA-Chip Pin 56 NET "MEINECLOCK" LOC = "P56"; ## IO_L05P_0 ist auf FPGA-Chip Pin 125 NET "MEINELED" LOC = "P125"; NET "MEINECLOCK" IOSTANDARD = LVCMOS25; NET "MEINELED" IOSTANDARD = LVCMOS33;

Code 0-4: Festlegung der Pinzuordnung und Pinkonfiguration in der Konfigurationsdatei blinkled.ucf

|

Schrittweise Erstellung

Hinweis: Die Analyse des Quelltextes finden Sie in dem nachfolgenden Kapitel.

blinkled.zip - Download des nachfolgenden Projektes, erstellt mit ISE von Xilinx, Version 9.1i.03

blinkled.zip - Download des nachfolgenden Projektes, erstellt mit ISE von Xilinx, Version 9.1i.03

Schritt 1: ISE starten

Siehe Kapitel 2.4

Bild 0-2: Sicht auf die ISE Entwicklungsumgebung nach dem Start.

Schritt 2: Neues Projekt anlegen

Bild 0-3: Neues Projekt anlegen.

Schritt 3: Projektname und Quelltextsprache (HDL) festlegen

Bild 0-4: Im Projekt Wizard: Projektname und Quelltextsprache (HDL) festlegen.

Schritt 4: Device festlegen

Bild 0-5: Im Projekt Wizard: Device spezifizieren, hier Spartan 3E, Typ XCS250E, Geschwindigkeitsstufe 4, Gehäuse TQ144.

Schritt 5: VHDL-Quelltextdatei anlegen

Bild 0-6: Im Projekt Wizard: VHDL-Quelltextdatei unter Angabe der Ein- und Ausgänge anlegen.

Bild 0-7: Im Projekt Wizard: Überblick zur automatisch erstellten Quelltextdatei-Vorlage.

Bild 0-8: Im Projekt-Browser: Sicht auf das automatisch erstellte Gerüst der Quelltextdatei samt automatisch eingefügter Libraries.

Schritt 6: Kodierung der VHDL-Datei

Bild 0-9: Kodierung der VHDL-Datei: Anpassung der eingefügten Libraries und Vervollständigen der Architektur.

Schritt 7: Synthese der VHDL-Datei

Bild 0-10: Um logische Programmierfehler zu entdecken kann bereits jetzt die Synthese aus der Quelltextdatei heraus angestoßen werden.

Bild 0-11: Anzeige in der unteren Konsole nach erfolgreicher Synthese.

Schritt 8: Zuordnung der Ein- und Ausgänge zu den physikalischen Pins

|

Bild 0-12: Erstellen einer dem VHDL-Quelltext blinkled.vhd zugeordnete Constraints-Datei blinkled.ucf

Man findet jetzt hierarchisch unterhalb von blinkled.vhd die noch leere Datei blinkled.ucf. Diese kann automatisiert generiert werden, oder von Hand ausgefüllt werden. Hier wird sie von Hand ausgefüllt, vergleiche die Angaben oben in der Projektübersicht zu den verwendeten Pins.

Bild 0-13: Fertig editierte Datei blinkled.ucf.

Schritt 9: Erstellen der Datei blinkled.bit

Um die Datei blinkled.bit zu generieren, die dann im letzten Schritt auf das Board geflasht wird, müssen alle drei Generierungsschritte der Reihe nach ausgeführt werden:

Bild 0-14: Generierung der datei blinkled.bit

Schritt 10: Vorbereiten des Boards

Bevor die Bit-Datei auf das Board geflasht wird, sollte die Beschaltung des DLP-FPGA-Boards sorgfältig und richtig vorgenommen werden.

Die folgenden Pin-Angaben beziehen sich auf das DLP-FPGA-Board, nicht auf den FPGA-Chip!

|

Bild 0-15: Beschaltung des DLP-FPGA-Boards für die Blink-LED-Anwendung.

Schritt 11: Flashen der Bit-Datei

|

Sie können mit usbview überprüfen, ob das DLP-Board für den PC sichtbar ist. Starten der Software, siehe Kapitel 2.3

Bild 0-16: Untersuchung der USB-Verbindung zwischen PC und DLP-FPGA-Board mittels usbview.