Übung - Testbench und D-Flip-Flop

(EN google-translate)

(PL google-translate)

Aufgabe 1

Test Sie die Testbench im Projekt aus Kapitel 7 "Testbench" mit Xilinx ISE 14.7.

Aufgabe 2

Schreiben Sie eine Testbench für das D-Flip-Flop aus dem vorangehenden Kapitel.

Aufgabe 3

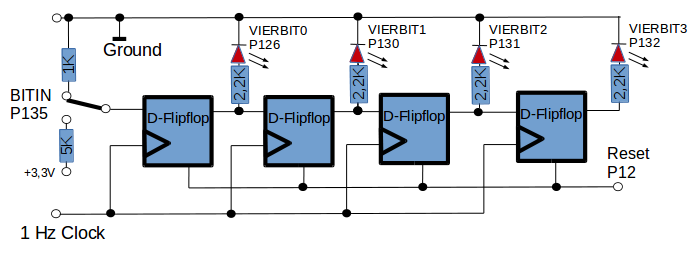

Es sollen vier D-Flip-Flops in Reihe geschaltet werden.

Das heißt der Ausgang Q0 des ersten Flip-Flops ist mit dem Eingang D1 des nachfolgenden verbunden usw.

Das Clock-Signal soll automatisch zyklisch mit 1Hz Taktrate für alle Flip-Flops gleichzeitig erfolgen.

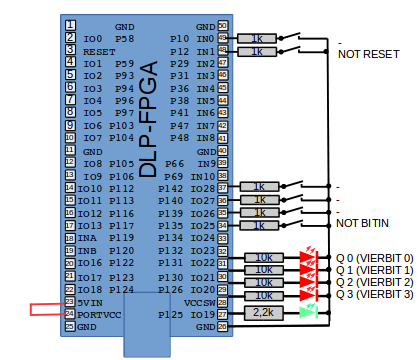

Das Reset-Signal soll gleichzeitig für alle Flip-Flops über einen externen Schalter bei P12 / IN1 erfolgen können (negative Logik wg. Pullup-Widerständen, s. vorangegangenes Kapitel).

Die Ausgänge Q0, Q1, Q2 und Q3 der vier Flip-Flops sollen mit vier LEDs an den Ausgängen IO20, 21, 22, 23 / P126, P130, P131, P132 verknüpft sein.

Der erste (freie) Eingang P0 soll mit negativer Logik über einen Eingang bei IO25 / P135 geschaltet werden können.

|

Zum Umgang mit Hardware

Gehen Sie insgesamt sorgfältig und verantwortungsbewußt mit der Ihnen überlassenen Hardware um!

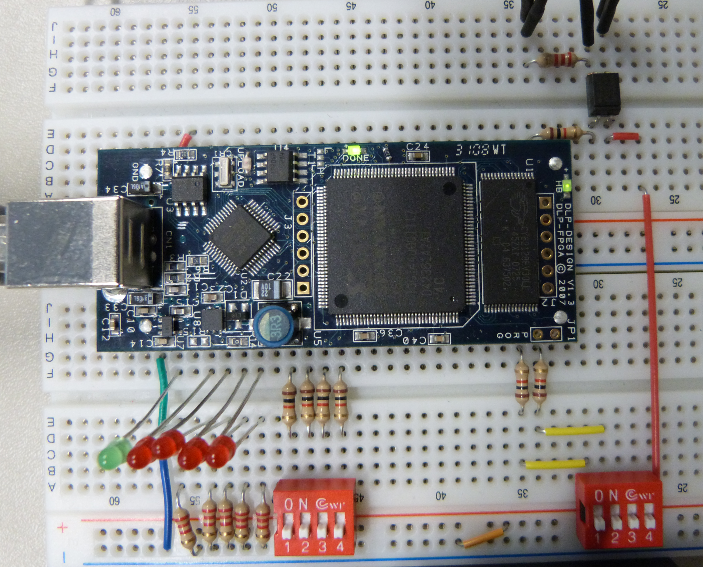

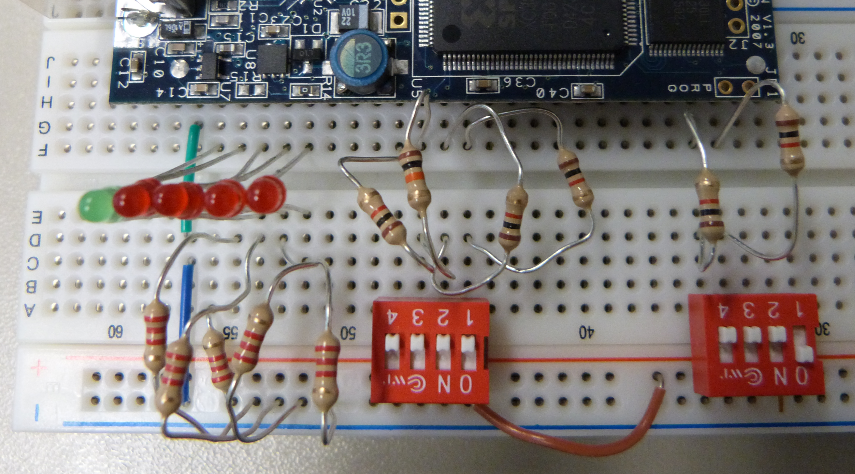

Bild 0-1: Gelungener Aufbau einer Schaltung auf einer Laborplatine.

Bild 0-2: Fehlerhafter Aufbau einer Schaltung auf einer Laborplatine.

Um das einwandfreie Funktionieren der auf der Laborplatine aufgebauten Schaltungen zu gewährleisten, sollte folgendes beachtet werden:

|

Gehen Sie insgesamt sorgfältig und verantwortungsbewußt mit der Ihnen überlassenen Hardware um!

Über das Scheitern

Bei der Kritik an dem fehlerhaften Schaltungsaufbau ist mehr im Spiel als ästhetische Erwägungen.

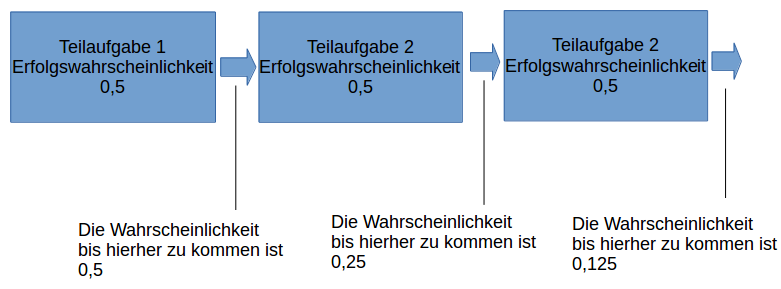

Es gibt stets viele Möglichkeiten mit einem Projekt zu scheitern.

Reduzieren Sie die Wahrscheinlichkeit für ein Scheitern durch sorgfältiges Arbeiten und die Aufteilung der Gedamtaufgabe in für sich überprüfbare Teile.

Bild 0-3: Verringerung der Erfolgsaussichten bei Teilprojekten, die voneinander abhängen.

Verringern Sie die Erfolgsaussichten eines Projekts nicht zusätzlich durch nachlässiges unverantwortliches Vorgehen.

Vergewissern Sie sich sorgfältig von der Korrektheit Ihrer Teilstrukturen und vermeiden Sie so die Versagenswahrscheinlichkeit bei nachfolgenden Schritten.

Lösung zu Aufgabe 3

schieberegister.zip - ISE9-Projekt zur Musterlösung von Aufgabe 3 (Schieberegister aus D-FlipFlops).

schieberegister.zip - ISE9-Projekt zur Musterlösung von Aufgabe 3 (Schieberegister aus D-FlipFlops).

Bild 0-4: Darstellung der in der Aufgabe verlangten Funktionalität als digitale Schaltung.

Hinweis: Die 1Hz-Clock wird im Programm wieder aus dem 6MHz-Eingang gewonnen.

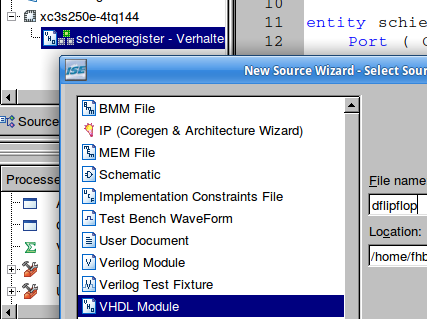

Hinweis: Es wird dem Hauptprogramm ein Unter-Quelltext beigefügt: Rechte Maustaste auf Hauptprogramm "New Source", "VHDL Module":

Bild 0-5: Erstellen des Unter-Quelltextes mit dem D-FlipFlop.

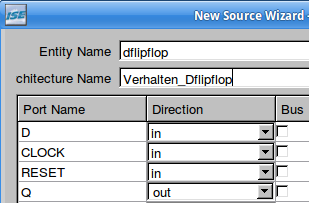

Bild 0-6: Erstellen des Unter-Quelltextes mit dem D-FlipFlop 2.

Bild 0-7: Zugehöriger Aufbau / Belegungen mit dem Testboard.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity schieberegister is

Port ( CLOCK6MHZ : in STD_LOGIC;

RESET : in STD_LOGIC;

BITIN : in STD_LOGIC;

VIERBIT : out STD_LOGIC_VECTOR (3 downto 0));

end schieberegister;

architecture Verhalten_Schieberegister of schieberegister is

signal sig_d : std_logic_vector (3 downto 0) := "0000";

signal sig_q : std_logic_vector (3 downto 0) := "0000";

signal clock1Hz : std_logic := '0';

signal all_reset : std_logic := '1';

signal zaehler : integer range 0 to 2999999 := 0;

begin

-- Erzeugen der 1Hz-Clock mit Hilfe eines Prozesses (vergl. Blink-LED)

process begin

wait until rising_edge(CLOCK6MHZ);

if (zaehler<2999999) then

zaehler <= zaehler+1;

else

zaehler <= 0;

clock1Hz <= not clock1Hz;

end if;

end process;

-- Vier D-FlipFlops instanziieren

FLIP3: entity dflipflop

port map(D => sig_d(3), CLOCK => clock1Hz, RESET => all_reset, Q => sig_q(3));

FLIP2: entity dflipflop

port map(D => sig_d(2), CLOCK => clock1Hz, RESET => all_reset, Q => sig_q(2));

FLIP1: entity dflipflop

port map(D => sig_d(1), CLOCK => clock1Hz, RESET => all_reset, Q => sig_q(1));

FLIP0: entity dflipflop

port map(D => sig_d(0), CLOCK => clock1Hz, RESET => all_reset, Q => sig_q(0));

-- Signalwege / Verbindungen laut Schaltplan beschreiben

-- Verbindungen zwischen den D-FlipFlops und zum Eingangsschalter

sig_d(0) <= not BITIN;

sig_d(1) <= sig_q(0);

sig_d(2) <= sig_q(1);

sig_d(3) <= sig_q(2);

-- Verbindungen zu den LEDs

VIERBIT(3) <= sig_q(3);

VIERBIT(2) <= sig_q(2);

VIERBIT(1) <= sig_q(1);

VIERBIT(0) <= sig_q(0);

end Verhalten_Schieberegister;

Code 0-1: schieberegister.vhd - VHDL-Quelltext des Hauptprogramms zum Schieberegister bestehend aus vier D-FlipFlops.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity dflipflop is

Port ( D : in STD_LOGIC;

CLOCK : in STD_LOGIC;

RESET : in STD_LOGIC;

Q : out STD_LOGIC);

end dflipflop;

architecture Verhalten_Dflipflop of dflipflop is

signal sig_d : std_logic := '0';

signal sig_clock : std_logic := '0';

signal sig_reset : std_logic := '0';

signal sig_q : std_logic := '0';

begin

process(sig_clock,sig_reset)

begin

if (sig_reset='1') then

sig_q <= '0';

elsif (sig_clock'event and sig_clock='1') then

sig_q <= sig_d;

end if;

end process;

sig_clock <= CLOCK;

sig_reset <= not RESET; -- inverse Logik wg. externer Pullup

sig_d <= D;

Q <= sig_q;

end Verhalten_Dflipflop;

Code 0-2: dflipflop.vhd - VHDL-Quelltext des Unterprogramms (Definition eines D-FlipFlops) zum Schieberegister bestehend aus vier D-FlipFlops.

## GCLK6 ist auf FPGA-Chip Pin 56 NET "CLOCK6MHZ" LOC = "P56"; NET "VIERBIT<3>" LOC = "P126"; NET "VIERBIT<2>" LOC = "P130"; NET "VIERBIT<1>" LOC = "P131"; NET "VIERBIT<0>" LOC = "P132"; NET "CLOCK6MHZ" IOSTANDARD = LVCMOS25; NET "VIERBIT<3>" IOSTANDARD = LVCMOS33; NET "VIERBIT<2>" IOSTANDARD = LVCMOS33; NET "VIERBIT<1>" IOSTANDARD = LVCMOS33; NET "VIERBIT<0>" IOSTANDARD = LVCMOS33; NET "RESET" LOC = "P12" | PULLUP | IOSTANDARD = LVCMOS33; NET "BITIN" LOC = "P135" | PULLUP | IOSTANDARD = LVCMOS33;

Code 0-3: schieberegister.ucf - Constraints-Datei.