Bitmuster-Vergleicher

(EN google-translate)

(PL google-translate)

Es soll eine logische Schaltung über VHDL formuliert werden, die zwei Bitmuster miteinander vergleicht und bei gleichen Mustern 1 liefert, sonst 0.

Die beiden Muster A und B bestehen hier nur aus jeweils zwei Bits. Die entsprechende Wahrheitstabelle ist:

| Bit A-1 | Bit A-0 | Bit B-1 | Bit B-0 | Ausgang C |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Tabelle 0-1: Logiktabelle Bitmuster-Vergleicher.

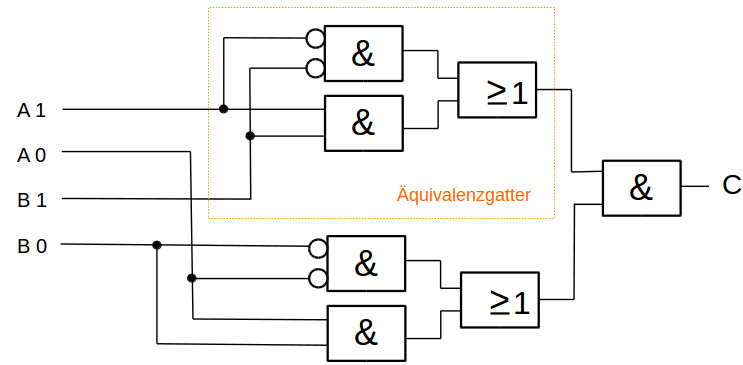

Eine Realisierung mit Logikbausteinen kann folgendermaßen erfolgen:

Bild 0-1: Realisierung mit Logikbausteinen.

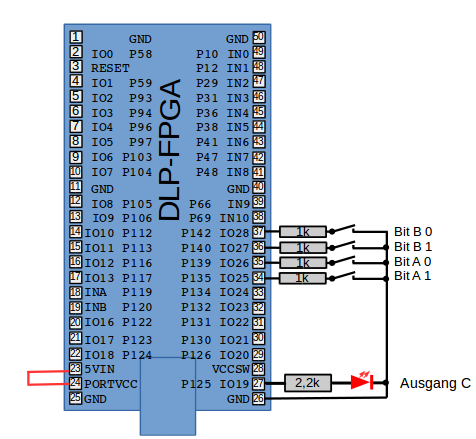

Auf dem DLP-FPGA-Board soll das System mittels vierer DIP-Schalter (Bits A-1, A-0, B-1, B-0) und einer Ausgangs-LED realisiert werden (Ausgang C):

Die DIP-Schalter schalten die Eingänge gegen Masse, da interne Pullup-Widerstände aktiviert werden.

Die physikalische Zuordnung der 4 Bits soll sein:

Bit A-1: IO25 P135 Bit A-0: IO26 P139 Bit B-1: IO27 P140 Bit B-0: IO28 P142 Ausgang C: IO19 P125

Code 0-1: Pinzuordnung

Die jeweils korrespondierenden Bits werden mit einem Äquivalenz-Logikbaustein verglichen. Die Ergebnisse aus den Äquivalenz-Logikbausteinen werden UND-Verknüpft.

| Bezeichner | Bedeutung |

|---|---|

| and | UND |

| nand | Negativ-UND |

| or | ODER |

| nor | Negativ-ODER |

| xor | Exklusiv Oder / Antivalenz |

| xnor | Negativ-Exklusiv Oder / Äquivalenz |

Tabelle 0-2: Logische Operatoren in VHDL.

| Bit 1 | Bit 0 | and | nand | or | nor | xor | xnor |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

Tabelle 0-3: Ausgang der verschiedenen logischen Operatoren bei zwei Bits als Eingang.

Operatoren haben in VHDL jeweils die gleiche Priorität, weshalb Klammerungen unabdingbar sind.

Projekt-Download

mustervergleich.zip - Download des Beispiels als ISE-Projekt.

mustervergleich.zip - Download des Beispiels als ISE-Projekt.

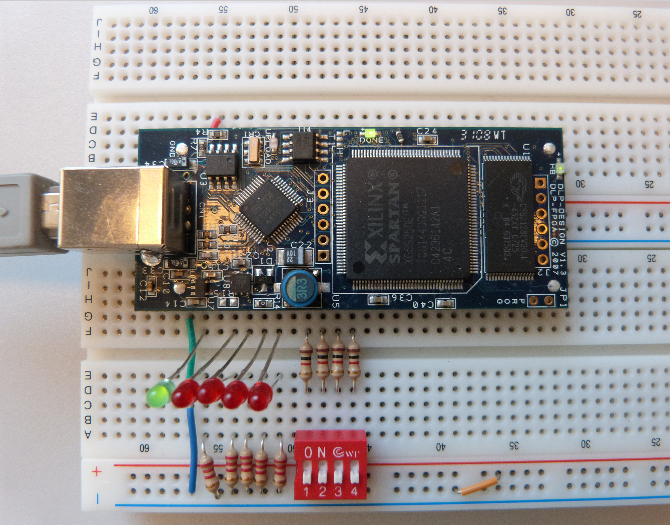

Beschaltung

Bild 0-2: Foto der gesamten Testschaltung. Alle nachfolgenden Programm-Varianten können damit getestet werden.

Bild 0-3: Äußere Beschaltung des DLP-FPGA-Boards.

Quelltext

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity mustervergleich is

Port ( A1 : in STD_LOGIC;

A0 : in STD_LOGIC;

B1 : in STD_LOGIC;

B0 : in STD_LOGIC;

C : out STD_LOGIC);

end mustervergleich;

architecture Behavioral of mustervergleich is

begin

C <= (A1 xnor B1) and (A0 xnor B0);

end Behavioral;

Code 0-2: Umsetzung mit VHDL in der Projektdatei mustervergleich.vhd

NET "A1" LOC = "P135" | PULLUP | IOSTANDARD = LVCMOS33 ; NET "A0" LOC = "P139" | PULLUP | IOSTANDARD = LVCMOS33 ; NET "B1" LOC = "P140" | PULLUP | IOSTANDARD = LVCMOS33 ; NET "B0" LOC = "P142" | PULLUP | IOSTANDARD = LVCMOS33 ; NET "C" LOC = "P125" | IOSTANDARD = LVCMOS33 | SLEW = SLOW ;

Code 0-3: Festlegung der Pinzuordnung und Pinkonfiguration in der Konfigurationsdatei mustervergleich.ucf

Version 2 - Automatischer Binärzähler

mustervergleich2.zip - Download des Beispiels als ISE-Projekt.

mustervergleich2.zip - Download des Beispiels als ISE-Projekt.

Bild 0-4: Beschaltung für diese Projektvariante.

Nun soll der Binärzähler automatisch hochzählen, statt Werte über die DIP-Schalter einzustellen.

Die Architektur mit den vielen Hilfsvariablen (signal) mag überflüssig aufwändig wirken,

aber beispielsweise kann der Ausgangsvektor VIERBIT nicht gelesen werden. D.h. man kann

damit keine Zuweisungen der Form x = VIERBIT(0); formulieren. Darum mußte der

Hilfsvektor wort eingeführt werden.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity mustervergleich2 is

Port ( MEINECLOCK : in STD_LOGIC;

MEINELED : out STD_LOGIC;

VIERBIT : out STD_LOGIC_VECTOR(3 downto 0)

);

end mustervergleich2;

-- Clock-In == 6MHz, Toggeln nach 3000000 Schritten ergibt 1Hz Blinkfrequenz.

architecture Behavioral of mustervergleich2 is

signal zaehler : integer range 0 to 2999999 := 0;

signal kleinerzaehler : integer range 0 to 15 := 0;

signal logikpegel : std_logic := '0';

signal wort : std_logic_vector(3 downto 0);

signal A1,A0,B1,B0,C : std_logic;

begin

process begin

wait until rising_edge(MEINECLOCK);

if (zaehler<2999999) then

zaehler <= zaehler+1;

else

zaehler <= 0;

logikpegel <= not logikpegel;

if (kleinerzaehler<15) then

kleinerzaehler <= kleinerzaehler+1;

else

kleinerzaehler <= 0;

end if;

end if;

end process;

wort <= conv_std_logic_vector(kleinerzaehler,VIERBIT'length);

A1 <= wort(0);

A0 <= wort(1);

B1 <= wort(2);

B0 <= wort(3);

C <= (A1 xnor B1) and (A0 xnor B0);

VIERBIT <= wort;

MEINELED <= C;

end Behavioral;

Code 0-4: Umsetzung mit VHDL in der Projektdatei mustervergleich2.vhd

## GCLK6 ist auf FPGA-Chip Pin 56 NET "MEINECLOCK" LOC = "P56"; ## IO_L05P_0 ist auf FPGA-Chip Pin 125 NET "MEINELED" LOC = "P125"; NET "VIERBIT<3>" LOC = "P126"; NET "VIERBIT<2>" LOC = "P130"; NET "VIERBIT<1>" LOC = "P131"; NET "VIERBIT<0>" LOC = "P132"; NET "MEINECLOCK" IOSTANDARD = LVCMOS25; NET "MEINELED" IOSTANDARD = LVCMOS33; NET "VIERBIT<3>" IOSTANDARD = LVCMOS33; NET "VIERBIT<2>" IOSTANDARD = LVCMOS33; NET "VIERBIT<1>" IOSTANDARD = LVCMOS33; NET "VIERBIT<0>" IOSTANDARD = LVCMOS33;

Code 0-5: Festlegung der Pinzuordnung und Pinkonfiguration in der Konfigurationsdatei mustervergleich2.ucf

Version 3 - Modularisierung

mustervergleich3.zip - Download des Beispiels als ISE-Projekt.

mustervergleich3.zip - Download des Beispiels als ISE-Projekt.

Hat man einmal eine etwas kompliziertere Architektur erstellt, die in verschiedenen Projekten gebraucht werden kann, so macht es Sinn, diese als ein Modul zu behandeln und deren Ein- und Ausgänge auf die Signale eines "Gastprojektes" zu mappen.

Die folgende Variante des Mustervergleichers soll demonstrieren wie dies in ISE-Projekten umgesetzt werden kann.

Das Modul vergleich wurde an den Beginn des gleichen Quelltextes gesetzt, wie

mustervergleich3.

In diesem Fall ist es nötig die LIBRARY und USE - Angaben für jeden Part zu wiederholen.

Zwei Instanzen des einfachen Bitvergleichers werden im zweiten Programmteil erzeugt.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- use IEEE.NUMERIC_STD.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity vergleich is

Port (

x : in STD_LOGIC;

y : in STD_LOGIC;

z : out STD_LOGIC

);

end vergleich;

architecture vergleich_arch of vergleich is

begin

z <= (x and y) or ((not x) and (not y));

end vergleich_arch;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- use IEEE.NUMERIC_STD.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity mustervergleich3 is

Port ( MEINECLOCK : in STD_LOGIC;

MEINELED : out STD_LOGIC;

VIERBIT : out STD_LOGIC_VECTOR(3 downto 0)

);

end mustervergleich3;

-- Clock-In == 6MHz, Toggeln nach 3000000 Schritten ergibt 1Hz Blinkfrequenz.

architecture Behavioral of mustervergleich3 is

signal zaehler : integer range 0 to 2999999 := 0;

signal kleinerzaehler : integer range 0 to 15 := 0;

signal logikpegel : std_logic := '0';

signal wort : std_logic_vector(3 downto 0);

signal A1,A0,B1,B0,C,C1,C0 : std_logic;

begin

process begin

wait until rising_edge(MEINECLOCK);

if (zaehler<2999999) then

zaehler <= zaehler+1;

else

zaehler <= 0;

logikpegel <= not logikpegel;

if (kleinerzaehler<15) then

kleinerzaehler <= kleinerzaehler+1;

else

kleinerzaehler <= 0;

end if;

end if;

end process;

wort <= conv_std_logic_vector(kleinerzaehler,VIERBIT'length);

A1 <= wort(0);

A0 <= wort(1);

B1 <= wort(2);

B0 <= wort(3);

--Zwei Instanzen des Vergleichers aus vergleicher.vhd

--erzeugen und Ein- und Ausgänge passend mappen:

--vergleicher1: entity work.vergleicher(vergleicher_arch)

vergleicher1: entity vergleich

port map(x => A1, y => B1, z => C1);

--vergleicher2: entity work.vergleicher(vergleicher_arch)

vergleicher2: entity vergleich

port map(x => A0, y => B0, z => C0);

C <= C1 and C0;

-- alte Version: C <= (A1 xnor B1) and (A0 xnor B0);

VIERBIT <= wort;

MEINELED <= C;

end Behavioral;

Code 0-6: Umsetzung mit VHDL in der Projektdatei mustervergleich3.vhd

## GCLK6 ist auf FPGA-Chip Pin 56 NET "MEINECLOCK" LOC = "P56"; ## IO_L05P_0 ist auf FPGA-Chip Pin 125 NET "MEINELED" LOC = "P125"; NET "VIERBIT<3>" LOC = "P126"; NET "VIERBIT<2>" LOC = "P130"; NET "VIERBIT<1>" LOC = "P131"; NET "VIERBIT<0>" LOC = "P132"; NET "MEINECLOCK" IOSTANDARD = LVCMOS25; NET "MEINELED" IOSTANDARD = LVCMOS33; NET "VIERBIT<3>" IOSTANDARD = LVCMOS33; NET "VIERBIT<2>" IOSTANDARD = LVCMOS33; NET "VIERBIT<1>" IOSTANDARD = LVCMOS33; NET "VIERBIT<0>" IOSTANDARD = LVCMOS33;

Code 0-7: Festlegung der Pinzuordnung und Pinkonfiguration in der Konfigurationsdatei mustervergleich3.ucf - identisch zu mustervergleich2.ucf