Echtzeitanwendungen auf Basis von HDL im Sommersemester 2026

(EN google-translate)

(PL google-translate)

|

04_SoSe2026 -- Einstiegsseite zum Sommersemester 2026 mit Angaben zu Räumen, Zeiten und den Prüfungen der einzelnen Fächer.

04_SoSe2026 -- Einstiegsseite zum Sommersemester 2026 mit Angaben zu Räumen, Zeiten und den Prüfungen der einzelnen Fächer.

#1 Di, 24.03.2026

THEMEN HEUTE

|

1. Worum geht es?

|

Sollte eine Steuereinheit oder ein regelungstechnisches System sehr schnell arbeiten, so musste es als elektronische Schaltung ausgeführt werden. Das Problem damit: Auch kleine Änderungen erfordern den Austausch der ganzen Schaltung und die Kombination mehrerer solcher Schaltungen gestaltet sich schwierig, da oft Ein- und Ausgänge unterschiedliche Impedanzen haben, oder schlicht die Datenblätter, die dies dokumentieren fehlen.

Ein FPGA arbeitet grob gesagt genau so wie eine digitale Schaltung, ist auch annähernd so schnell, jedoch wird die Schaltung, die auf dem FPGA laufen soll als Programmquelltext in einer besonderen Programmiersprache vorgegeben. Ein Compiler übernimmt dann die Aufgabe, die Logik dieses Programms in Verknüpfungen elementarer Logikbausteine auf dem FPGA umzusetzen und auf den FPGA zu übertragen.

2. Motivation -- Warum ist das wichtig?

FPGA finden ein breites Einsatzfeld in zivilen und militärischen Anwendungen, bei denen ein eingebettes System mit einer sehr hohen Performance gebraucht wird, um beispielsweise eine regelungstechnische Aufgabe zu lösen. Man findet FPGA-Lösungen in den eingebetteten Systemen von...

|

3. Welche Themen werden behandelt?

|

4. Welche Leistungen sollten Sie erbringen? / Organisatorisches

Die Prüfung ist semesterbegleitend, heißt, es gibt einen E-Test (elektronische Klausur) mit Praxiselementen: Sie beantworten als Prüfung einerseits theoretische Fragen, lösen andererseits aber auch eine praktische Aufgabe, bei der eine Schaltung aufgebaut und ein VHDL-Programm geschrieben und getestet werden soll. Diese Prüfung findet am letzten Vorlesungstermin statt. Im Vorfeld besteht ausraichend Zeit, die notwendigen Fertigkeiten zu erlernen.

5. Einstieg

|

69_FPGA/01_Einfuehrung -- Wie ist ein FPGA aufgebaut und wie programmiert man ihn?

69_FPGA/01_Einfuehrung -- Wie ist ein FPGA aufgebaut und wie programmiert man ihn?

Übersicht zum CMOD S7: 69_FPGA/23_VIVADO

Übersicht zum CMOD S7: 69_FPGA/23_VIVADO

Einstiegsprojekt mit VIVADO Schritt für Schritt: 69_FPGA/23_VIVADO/02_Startprojekt

Einstiegsprojekt mit VIVADO Schritt für Schritt: 69_FPGA/23_VIVADO/02_Startprojekt

6. Hands on -- Die erste Übung

|

Einstiegsprojekt mit VIVADO Schritt für Schritt: 69_FPGA/23_VIVADO/02_Startprojekt

Einstiegsprojekt mit VIVADO Schritt für Schritt: 69_FPGA/23_VIVADO/02_Startprojekt

#2 Di, 31.03.2026

Themen heute:

|

1. Quiz

|

2. Anmerkungen zur VHDL-Syntax

VHDL-Syntax: 69_FPGA/11_VHDL

VHDL-Syntax: 69_FPGA/11_VHDL

3. Bitvergleicher mit dem CMOD S7

Unter nachfolgendem Link ist ein Bitvergleicher mit 2 mal 2 Eingängen dargestellt, wie er mit dem DSP FPGA realisiert wurde:

69_FPGA/05_Beispiele/03_Mustervergleich

69_FPGA/05_Beispiele/03_Mustervergleich

|

ÜBUNG

|

4. Blinkende LED mit dem CMOD S7

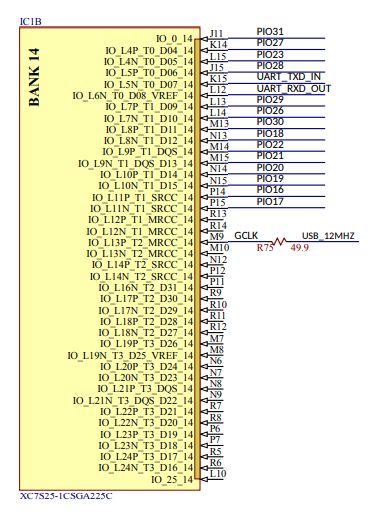

In dem Beispielfile für alle möglichen Constraint Varianten, findet sich ein Eintrag für die Aktivierung einer 12MHz Taktquelle:

# 12 MHz System Clock

set_property -dict { PACKAGE_PIN M9 IOSTANDARD LVCMOS33 } [get_ports { clk }]; #IO_L13P_T2_MRCC_14 Sch=gclk

create_clock -add -name sys_clk_pin -period 83.33 -waveform {0 41.66} [get_ports { clk }];

Code 0-1: Eintrag für die Aktivierung einer 12MHz Taktquelle.

Im Pinlayout des Datenblatts für den CMOD S7 ist sichtbar, wo die 12MHz Taktquelle in den FPGA geführt wird:

Bild 0-1: Auszug aus dem Pinlayout des Datenblatts für den CMOD S7.

Auf der Basis des DSP FPGA sah eine Blinkschaltung folgendermaßen aus:

69_FPGA/05_Beispiele/01_Blinkende_LED

69_FPGA/05_Beispiele/01_Blinkende_LED

ÜBUNG

|

69_FPGA/23_VIVADO/02_Startprojekt

69_FPGA/23_VIVADO/02_Startprojekt

Di, 07.04.2026 -- keine Lehrveranstaltung wegen Ostern

#3 Di, 14.04.2026

AUFGABE 1

|

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity and_gate is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

C : out STD_LOGIC);

end and_gate;

architecture Behavioral of and_gate is

begin

C <= A and B;

end Behavioral;

Code 0-2: VHDL-Code zum UND-Gatter.

NET "A" LOC = "P139" | PULLUP | IOSTANDARD = LVCMOS33 ; NET "B" LOC = "P135" | PULLUP | IOSTANDARD = LVCMOS33 ; NET "C" LOC = "P131" | IOSTANDARD = LVCMOS33 | SLEW = SLOW ;

Code 0-3: Constraints (.ucf-Datei) zum UND-Gatter.

Beachten Sie die Pullup-Einträge bei den Eingängen (Besprechung im Unterricht).

|

#4 Di, 21.04.2026

Themen heute:

|

1. Verwendung von Konstanten

69_FPGA/11_VHDL

69_FPGA/11_VHDL

2. Ansteuerung einer 7-Segment-Anzeige

69_FPGA/22_Uebung

69_FPGA/22_Uebung

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity lauflicht is

Port ( MEINECLOCK : in STD_LOGIC;

LEDS : out STD_LOGIC_VECTOR (6 downto 0));

end lauflicht;

architecture Behavioral of lauflicht is

signal zaehler : integer range 0 to 2999999 := 0; -- 20 kHz

signal zaehler2 : integer range 0 to 9 := 0; -- 200 Hz

signal wort : std_logic_vector(6 downto 0);

begin

process(MEINECLOCK)

begin

if rising_edge(MEINECLOCK) then

-- erster Zähler

if zaehler < 2999999 then

zaehler <= zaehler + 1;

else

zaehler <= 0;

-- zweiter Zähler

if zaehler2 < 9 then

zaehler2 <= zaehler2 + 1;

else

zaehler2 <= 0;

end if;

end if;

end if;

end process;

-- 7-Segment-Codierung

with zaehler2 select

wort <=

"1111110" when 0,

"0110000" when 1,

"1101101" when 2,

"1111001" when 3,

"0110011" when 4,

"1011011" when 5,

"1111101" when 6,

"1110001" when 7,

"1111111" when 8,

"1110011" when 9,

"1000000" when others;

LEDS <= wort;

end Behavioral;

Code 0-4: Studentische Lösung.

#5 Di, 28.04.2026

Es soll die Theorie zur Implementierung Neuronaler Netze mit FPGAs heute gelegt werden, aber noch nicht praktisch umgesetzt werden. Statt dessen folgen danach noch einmal "konventionelle" Übungen.

Themen heute:

|

1. Softcomputing

ÜBERBLICK

Fuzzy-Logik und Fuzzy-Regler -- 67_Echtzeitsysteme/13_Fuzzy

Fuzzy-Logik und Fuzzy-Regler -- 67_Echtzeitsysteme/13_Fuzzy

Neuronale Netze -- 67_Echtzeitsysteme/08_NeuronaleNetze

Neuronale Netze -- 67_Echtzeitsysteme/08_NeuronaleNetze

Deep Learning -- 79_Deep_Learning/02_TicTacToe/03_SDA

Deep Learning -- 79_Deep_Learning/02_TicTacToe/03_SDA

Motivation

2. Anfänge der KI

3. Neuronale Netze

67_Echtzeitsysteme/08_NeuronaleNetze/01_Neuron

67_Echtzeitsysteme/08_NeuronaleNetze/01_Neuron

4. Belernen von Neuronalen Netzen

67_Echtzeitsysteme/08_NeuronaleNetze/02_Backpropagation

67_Echtzeitsysteme/08_NeuronaleNetze/02_Backpropagation

5. Neuronale Netze mit FPGAs

6. Verwendung von Konstanten

69_FPGA/11_VHDL

69_FPGA/11_VHDL

##### UMSETZUNG IM LETZTEN JAHR #####

3. Überlegungen zu Kapazität und Potential des Konzepts und Möglichkeiten zur Reduktion

Laut der aufgegebenen Statistik wurden 2% der Ressourcen verbraucht, somit bietet der verwendete FPGA das Potential ein Neuronales Netz diesen Typs mit maximal 150 Neuronen aufzubauen.

Welche Möglichkeiten gäbe es, die Anzahl der implementierbaren Neuronen zu erhöhen?

MUSTERLÖSUNG NXOR mittels Neuronalem Netz-Derivat auf FPGA

NeuroNetzNXOR.zip -- Xilinx-Projekt: MUSTERLÖSUNG zur Generierung eines Netzes mit nur 2 Bit Ausgangswertebereich pro Neuron.

NeuroNetzNXOR.zip -- Xilinx-Projekt: MUSTERLÖSUNG zur Generierung eines Netzes mit nur 2 Bit Ausgangswertebereich pro Neuron.

Hinweis:

Statt direkt

u0 <= (((w0*in0)/2)+((w1*in1)/2))/8;

...wurde

xu0 <= w0*in0;

yu0 <= w1*in1;

u0 <= ((xu0/2)+(yu0/2))/8;

implementiert, da sonst beim Kompilieren eine Warnung

zu einem möglichen Datenverlust angezeigt wurde.

Code 0-5: Hinweis.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity NeuroNetzNXOR is

Port ( inputA : in STD_LOGIC;

inputB : in STD_LOGIC;

outputC : out STD_LOGIC);

end NeuroNetzNXOR;

architecture Behavioral of NeuroNetzNXOR is

-- Konstanten einfügen:

constant w0: integer := -6;

constant w1: integer := -2;

constant w2: integer := 2;

constant w3: integer := 2;

constant w4: integer := -1;

constant w5: integer := -4;

constant l0: integer := -8;

constant l1: integer := 6;

constant l2: integer := -4;

constant l3: integer := -5;

constant l4: integer := 1;

constant l5: integer := 2;

constant l6: integer := -7;

constant l7: integer := -7;

constant l8: integer := 1;

constant l9: integer := -3;

constant l10: integer := -1;

constant l11: integer := -1;

constant l12: integer := -4;

constant l13: integer := 2;

constant l14: integer := 3;

constant l15: integer := 3;

constant l16: integer := 0;

constant l17: integer := 2;

constant l18: integer := 4;

constant l19: integer := -6;

constant l20: integer := -6;

constant l21: integer := 4;

constant l22: integer := -6;

constant l23: integer := -4;

constant l24: integer := -1;

constant l25: integer := -4;

constant l26: integer := 3;

constant l27: integer := -8;

constant l28: integer := 4;

constant l29: integer := -5;

constant l30: integer := -1;

constant l31: integer := -6;

constant l32: integer := -1;

constant l33: integer := 3;

constant l34: integer := -1;

constant l35: integer := 0;

constant l36: integer := -7;

constant l37: integer := 6;

constant l38: integer := 7;

constant l39: integer := 7;

constant l40: integer := -8;

constant l41: integer := -6;

constant l42: integer := 4;

constant l43: integer := -8;

constant l44: integer := -2;

constant l45: integer := -4;

constant l46: integer := 7;

constant l47: integer := 2;

-- Eingangssignale definieren:

signal in0 : integer range -8 to 7 := 0; -- 4Bit Variable

signal in1 : integer range -8 to 7 := 0; -- 4Bit Variable

-- Ergebnisse der gewichteten Summen definieren:

-- wegen int u0 = ( ((w0*in0)/2) + ((w1*in1)/2) )/8; // [-7,8]

-- kann u0 theoretisch als Zwischenergebnis maximal 16*7=112, bzw. minimal -16*8=128 annehmen.

-- Darum wird als Bereich der einer vorzeichenbehafteten 8-Bit-Integerzahl gewählt:

signal u0 : integer range -127 to 128 := 0; -- 8Bit Variable

signal u1 : integer range -127 to 128 := 0; -- 8Bit Variable

signal u2 : integer range -127 to 128 := 0; -- 8Bit Variable

-- Ausgänge der Neuronen definieren:

signal out0 : integer range -8 to 7 := 0; -- 4Bit Variable

signal out1 : integer range -8 to 7 := 0; -- 4Bit Variable

signal out2 : integer range -8 to 7 := 0; -- 4Bit Variable

-- Testweise Zwischenergebnisse berechnen und in Hilfsvariablen speichern:

-- Hilfsvariablen wegen warning, s.u.:

signal xu0 : integer range -127 to 128 := 0; -- 8Bit Variable

signal yu0 : integer range -127 to 128 := 0; -- 8Bit Variable

signal xu1 : integer range -127 to 128 := 0; -- 8Bit Variable

signal yu1 : integer range -127 to 128 := 0; -- 8Bit Variable

signal xu2 : integer range -127 to 128 := 0; -- 8Bit Variable

signal yu2 : integer range -127 to 128 := 0; -- 8Bit Variable

begin

-- Aus den logischen Eingängen die Neuronen-Inputs gewinnen:

-- Eingänge invertieren, wg. Pullup

in0 <= 7 when (inputA = '0') else -8;

in1 <= 7 when (inputB = '0') else -8;

-- Berechnung der gewichteten Summen

xu0 <= w0*in0;

yu0 <= w1*in1;

u0 <= ((xu0/2)+(yu0/2))/8;

-- WARNING ohne Hilfsvariablen:

-- line 114: The result of a 4x4-bit multiplication is partially used.

-- Only the 7 least significant bits are used. If you are doing this on purpose,

-- you may safely ignore this warning. Otherwise,

-- make sure you are not losing information, leading to unexpected circuit behavior.

xu1 <= w2*in0;

yu1 <= w3*in1;

u1 <= ( (xu1/2) + (yu1/2) )/8;

-- Lookup-Tabellen um aus u0 out0, bzw. aus u1 out1 zu bestimmen:

with u0 select out0 <=

l0 when -7,

l1 when -6,

l2 when -5,

l3 when -4,

l4 when -3,

l5 when -2,

l6 when -1,

l7 when 0,

l8 when 1,

l9 when 2,

l10 when 3,

l11 when 4,

l12 when 5,

l13 when 6,

l14 when 7,

l15 when others;

with u1 select out1 <=

l16 when -7,

l17 when -6,

l18 when -5,

l19 when -4,

l20 when -3,

l21 when -2,

l22 when -1,

l23 when 0,

l24 when 1,

l25 when 2,

l26 when 3,

l27 when 4,

l28 when 5,

l29 when 6,

l30 when 7,

l31 when others;

-- Behandlung der zweiten Neuronenschicht (nur ein Neuron):

xu2 <= w4*out0;

yu2 <= w5*out1;

u2 <= ( (xu2/2) + (yu2/2) )/8;

-- Lookup-Tabelle, um aus u2 out2 zu bestimmen:

with u2 select out2 <=

l32 when -7,

l33 when -6,

l34 when -5,

l35 when -4,

l36 when -3,

l37 when -2,

l38 when -1,

l39 when 0,

l40 when 1,

l41 when 2,

l42 when 3,

l43 when 4,

l44 when 5,

l45 when 6,

l46 when 7,

l47 when others;

-- Umwandlung des Integer-Ausgangssignals von out2 in den logischen Ausgang outputC:

with out2 select outputC <=

'0' when -8 to 0,

'1' when others;

end Behavioral;

Code 0-6: VHDL-Datei.

NET "inputA" LOC = "P126" | PULLUP | IOSTANDARD = LVCMOS33 ; NET "inputB" LOC = "P130" | PULLUP | IOSTANDARD = LVCMOS33 ; NET "outputC" LOC = "P125" | IOSTANDARD = LVCMOS33 | SLEW = SLOW ;

Code 0-7: Constraints-Datei.

Der entsprechende Testaufbau konnte erfolgreich getestet werden.

Laut der aufgegebenen Statistik wurden 2% der Ressourcen verbraucht, somit bietet der verwendete FPGA das Potential ein Neuronales Netz diesen Typs mit maximal 150 Neuronen aufzubauen.

MUSTERLÖSUNG zur Generierung eines Netzes mit nur 2 Bit Ausgangswertebereich pro Neuron

FPGA_NEURON_004_out4bit.zip -- Projekt: MUSTERLÖSUNG zur Generierung eines Netzes mit nur 2 Bit Ausgangswertebereich pro Neuron

FPGA_NEURON_004_out4bit.zip -- Projekt: MUSTERLÖSUNG zur Generierung eines Netzes mit nur 2 Bit Ausgangswertebereich pro Neuron

//004: Output nur 2 statt 4 Bit

import java.util.Random;

Random zzz = new Random(0);

public int zufall()

{

return zzz.nextInt(16)-8; // [-8,7]

}

public double fehler(int[] gen)

{

int out0 = netz(-8,-8,gen);

int out1 = netz(-8,7,gen);

int out2 = netz(7,-8,gen);

int out3 = netz(7,7,gen);

int err = (out0-7)*(out0-7) + (out1+8)*(out1+8) + (out2+8)*(out2+8) + (out3-7)*(out3-7);

return Math.sqrt((double)err);

}

public int netz(int in0, int in1, int[] gen)

{

int w0=gen[0]; int w1=gen[1]; int w2=gen[2]; int w3=gen[3]; int w4=gen[4]; int w5=gen[5];

// -8,7 => min -8*7=-56, max -8*-8=64 , /64=-1..2 == 2Bit!!

int u0 = ( (w0*in0) + (w1*in1) )/64; // [-1,2]

int u1 = ( (w2*in0) + (w3*in1) )/64;

u0+=1; // [0..3]

int out0 = gen[6+u0];

u1+=1; // [0..3]

int out1 = gen[6+4+u1];

int u2 = ( (w4*out0) + (w5*out1) )/64;

u2+=1; // [0..3]

int out2 = gen[6+4+4+u2];

return out2;

}

public void setup()

{

int[] gen = new int[18]; //6+16+16+16=54, 6+4+4+4=18

int[] genN = new int[18];

for(int i=0;i<gen.length;i++)

gen[i]=zufall();

for(int DURCHLAUF=0;DURCHLAUF<900;DURCHLAUF++)

{

int a = zzz.nextInt(gen.length);

int b = gen[a];

double bb=fehler(gen);

gen[a]=zufall();

double cc = fehler(gen);

if(bb<cc)

{

gen[a]=b;

}

else

{

if(cc<bb)

println("err="+cc);

}

}

double aktueller_fehler = fehler(gen);

println("err="+aktueller_fehler);

println();

// Codegenerator als Unterstützung für die Erstellung des FPGA-Programms

String EINRUECKUNG = " ";

// constant w0: integer := -77;

for(int i=0;i<6;i++)

println(EINRUECKUNG+"constant w"+i+": integer := "+gen[i]+";");

for(int i=0;i<12;i++)

println(EINRUECKUNG+"constant l"+i+": integer := "+gen[6+i]+";");

println();

println(EINRUECKUNG+"with u0 select out0 <=");

for(int i=0;i<3;i++)

println(EINRUECKUNG+"l"+i+" when "+(i-1)+", ");

println(EINRUECKUNG+"l3 when others;");

println();

println(EINRUECKUNG+"with u1 select out1 <=");

for(int i=0;i<3;i++)

println(EINRUECKUNG+"l"+(4+i)+" when "+(i-1)+", ");

println(EINRUECKUNG+"l7 when others;");

println();

println(EINRUECKUNG+"with u2 select out2 <=");

for(int i=0;i<3;i++)

println(EINRUECKUNG+"l"+(8+i)+" when "+(i-1)+", ");

println(EINRUECKUNG+"l11 when others;");

}

public void draw()

{

}

Code 0-8: MUSTERLÖSUNG zur Generierung eines Netzes mit nur 2 Bit Ausgangswertebereich pro Neuron

err=15.297058540778355

err=15.033296378372908

err=14.594519519326424

err=13.892443989449804

err=12.884098726725126

err=9.055385138137417

err=6.324555320336759

err=2.8284271247461903

err=0.0

err=0.0

constant w0: integer := 1;

constant w1: integer := 5;

constant w2: integer := 7;

constant w3: integer := 5;

constant w4: integer := -8;

constant w5: integer := 6;

constant l0: integer := 7;

constant l1: integer := 6;

constant l2: integer := -3;

constant l3: integer := -6;

constant l4: integer := -4;

constant l5: integer := -1;

constant l6: integer := -3;

constant l7: integer := -8;

constant l8: integer := 7;

constant l9: integer := -8;

constant l10: integer := 5;

constant l11: integer := -4;

with u0 select out0 <=

l0 when -1,

l1 when 0,

l2 when 1,

l3 when others;

with u1 select out1 <=

l4 when -1,

l5 when 0,

l6 when 1,

l7 when others;

with u2 select out2 <=

l8 when -1,

l9 when 0,

l10 when 1,

l11 when others;

Code 0-9: Ausgabe des Optimierers und Code-Generators.

##### ENDE UMSETZUNG IM LETZTEN JAHR #####

AUFGABE 1

|

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity and_gate is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

C : out STD_LOGIC);

end and_gate;

architecture Behavioral of and_gate is

begin

C <= A and B;

end Behavioral;

Code 0-10: VHDL-Code zum UND-Gatter.

NET "A" LOC = "P139" | PULLUP | IOSTANDARD = LVCMOS33 ; NET "B" LOC = "P135" | PULLUP | IOSTANDARD = LVCMOS33 ; NET "C" LOC = "P131" | IOSTANDARD = LVCMOS33 | SLEW = SLOW ;

Code 0-11: Constraints (.ucf-Datei) zum UND-Gatter.

Beachten Sie die Pullup-Einträge bei den Eingängen (Besprechung im Unterricht).

|

AUFGABE 2

Variieren Sie das Beispiel mit der blinkenden LED so, dass diese nun mit 4 Hertz blinkt.

AUFGABE 3

Versuchen Sie ein Programm und eine zugehörige Schaltung zu realisieren, bei der über zwei Eingänge A und B die Blinkfrequenz einer LED gesteuert werden kann:

|

#6 Di, 05.05.2026

Themen heute:

|

HINWEISE:

|