|

I2C - Inter IC-Bus mit dem ATmega32

Allgemeines

- Bei den AVR Mikrocontrollern wird die I2C-Schnittstelle als TWI-Schnittstelle bezeichnet (Two-Wire serial Interface).

- Diese Schnittstelle dient vor allem dazu nahe beieinander liegende (Dezimeterbereich) Komponenten einer Baugruppe miteinander zu verbinden.

- Sie ist relativ langsam (maximale Taktrate 100kHz), dafür benötigt sie nur zwei Leitungen.

- Dies ermöglicht einerseits einen unkomplizierten Aufbau.

- Zum anderen werden wenige andere Pins an den Mikrocontrollern okkupiert.

|

Anwendungsbereiche

- Viele fertige Baugruppen, insbesondere Sensoren und Anzeigelemente werden heute mit I2C-Bus angeboten.

- Oft liefern diese im Falle von Sensoren eine höhere Auflösung als z.B. ein parallel verfügbarer PWM-Ausgang.

- Aber auch um Rechenleistung und verfügbare interne Peripherie zu vergrößern, können auch mehrere Mikrocontroller miteinander verbunden werden.

|

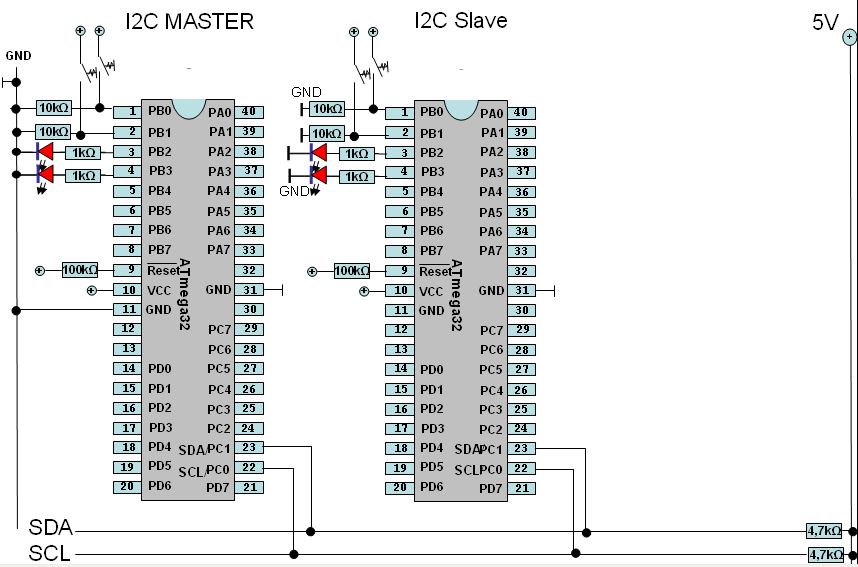

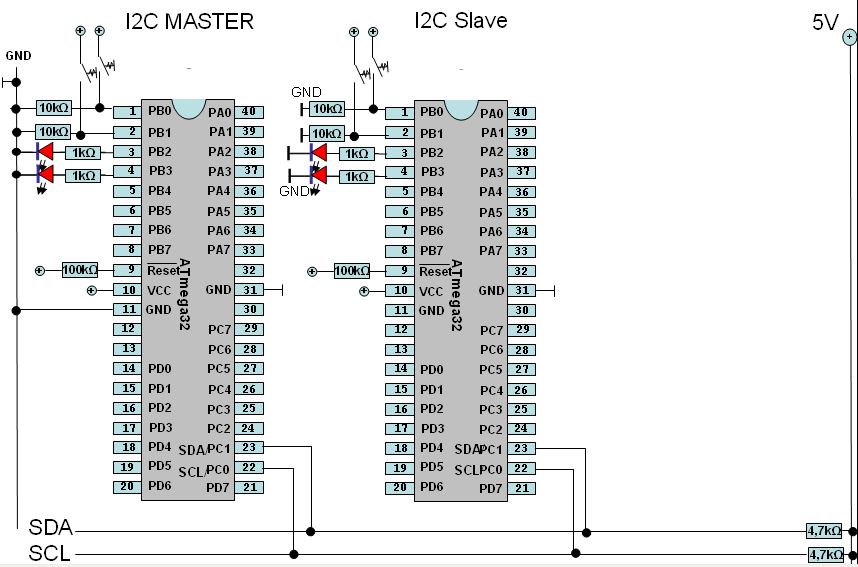

Anschluß der Busteilnehmer

- Die Baugruppen werden parallel an den Bus angeschlossen.

- Es sollten Abschlußwiderstände an den beiden Leitungen SDA (Daten) und SCL (Takt) gegen +5V von 4,7kΩ angeschlossen werden.

- Alternativ zu Abschlußwiderständen könnten auch die internen Pullup-Widerstände der Mikrocontroller aktiviert werden.

- Bei Verbindung zweier ATmega32 sähe die Anordnung folgendermaßen aus:

|

Bild 0-1: Testanordnung: I2C-Verbindung dreier ATmega32.

- Die obige Testanordnung sieht für jeden Baustein noch zwei Taster und LEDs vor, um kleine Versuche zur Datenübertragung zwischen den Bausteinen auslösen und anzeigen zu können.

|

I2C Protokoll

- Bei I2C hat immer genau ein Master Teilnehmer die Kontrolle über den Bus.

- Er spricht die angeschlossenen Client-Teilnehmer über deren Adressen an mit der Zusatzinformation, ob sie an den Master Daten senden sollen, oder vom Master Daten empfangen sollen.

- Der die Bytes empfangende Part muß mit einem ACK-Signal (Acknowledge) den Empfang quittieren.

- Die SCL-Leitung dient dazu den Takt für die über die SDL-Leitung übertragenen Daten vorzugeben.

- Änderungen an den Pegeln der Datenleitung SDA sind nur während der Low-Phasen der Taktleitung erlaubt.

- Vor und nach einer Anforderung des Masters und der Kommunikation mit einem Client, sind SCL und SDA im Zustand HIGH.

|

- Es werden bei I2C vier Modi unterschieden:

- MT - Master Transmitter

- MR - Master Receiver

- ST - Slave Transmitter

- SR - Slave Receiver

- Die im Slave-Modus arbeitenden Komponenten müssen Adressen erhalten, um von dem Master angesprochen werden zu können.

- Dabei ist die Adresse 0 ausgenommen, sie ist reserviert für den "General Call", bei dem eine Nachricht an alle Busteilnehmer geschickt wird, die den GC erlaubt haben.

|

Beteiligte Register beim ATmega32

|

Registerbezeichnung |

Bedeutung |

Beschreibung |

|

TWCR |

TWI Control Register |

Auslösen der verschiedenen Bus-Aktionen |

|

TWAR |

TWI Slave Adress Register |

Festlegung der Slave-Adresse des betreffenden Bausteins |

|

TWDR |

TWI Daten Register |

Register für die zu sendenden Daten, sowie Ort, in dem empfangene Daten gespeichert werden. |

|

TWSR |

TWI Status Register |

Informationsregister über Fortgang und Funktionieren der Übertragung, sowie Festlegen der Taktvorteilung. |

|

TWBR |

TWI Bitrate Register |

Enthält die Vorteilung der Taktfrequenz für die Datenübertragung. |

Tabelle 0-1: Beteiligte Register beim ATmega32

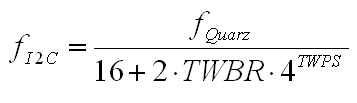

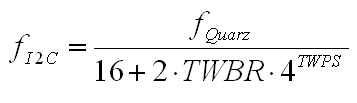

- Im C oder C++ - Programm kann die bitweise Datenübertragungsfrequenz folgendermaßen eingestellt werden:

|

Bild 0-2: Bestimmung der bitweisen Datenübertragungsfrequenz.

- Dabei wird TWPS automatisch in die unteren beiden Bits des Status-Registers übertragen, kann also nur 0,1,2 oder 3 sein.

- TWBR sollte laut Datenblatt auf 10 oder höher eingestellt werden, wenn der Baustein als Master arbeiten soll.

- TWBR kann Werte zwischen 0 und 255 annehmen.

- Bei einer Quarztaktfrequenz von 9,216MHz erreicht man für TWBR = 48 und TWPS = 1 eine Übertragungsrate von 23040 Bits pro Sekunde.

- Diese Rate liegt weit unter der maximalen von 100kHz und wird hier zunächst verwendet.

|

Beispielprogramme - Konzept

- Da SCL und SDA auf PC0 und PC1 von PORTC liegen, kann die Anzeige der Testboards nicht verwendet werden.

- Ersatzweise werden bei zwei Boards jeweils zwei LEDs an PB2 und PB3 angeschlossen.

- Das erste Board wird als TWI-Master konfiguriert, das zweite als Slave.

- Vier Testprogramme sollen entwickelt werden:

|

- Mit Taster PB0 ausgelöst ein Byte vom Master an den Slave senden, wobei mit Taster PB1 die zu sendende Zahl eingestellt wird (0..3, da nur zwei LEDs zur Anzeige vorhanden sind).

- Wie 1. aber zwei Byte übertragen.

- Mit Taster PB0 beim Master veranlassen, dass der Slave ein Byte an den Master sendet. Beim Slave wird mit Taster PB1 auf dem Slave die zu sendende Zahl eingestellt.

- Wie 3. aber zwei Byte übertragen.

|

Einzelheiten bei der Benutzung der TWI-Schnittstelle beim ATmega32

- Diese Testprogramme werden in den folgenden Unterkapiteln dargestellt.

- Zusammenfassend ist noch folgendes bei der Verwendung des TWI-Busses zu berücksichtigen:

|

Status-Register TWSR

- Im Status-Register TWSR kann Erfolg und Mißerfolg jeder Aktion, die auf dem Bus läuft abgelesen werden.

- Auf diese Möglichkeit wird, um die Programme einfach zu halten, bei den folgenden Programmen verzichtet.

- Ein Beispiel, wie das TWSR zur Feststellung von Übertragungsfehlern eingesetzt werden kann, findet sich im Datenblatt der Firma Atmel für den ATmega32.

- Sobald ein Slave sowohl Daten empfagen, als auch liefern soll, kommt man aber um die Verwendung des Statusregisters nicht herum, da hier abgelesen werden kann, ob die Anfrage eines Masters eine Lese- oder Schreibanfrage ist.

|

Adressregister TWAR

- Im Gegensatz zum SPI-Bus benötigt der I2C-Bus auch bei mehreren Clients nur zwei Leitungen, da die Adresse des anzusprechenden Slaves vom Master über den Bus gesendet wird.

- Achtung: Die Adresse eines Slaves, die bei diesem im Register TWAR eingestellt wird, wird dort um ein Bit nach links geshiftet gespeichert.

- Achtung: Ebenso um ein Bit geshiftet wird im Datenregister des Masters die Slaveadresse gespeichert und im ersten Bit die Information darüber, ob der Master Daten an den Slave sendet (0) oder vom Slave empfängt (1).

|

Acknowledge

- Bei Übertragung mehrerer Bytes quittiert der empfangende Part bei der Kommunikation in der Regel den Empfang eines Bytes mit einer Acknowledge-Nachricht.

|

Abfolge der Bus-Aktivitäten bei den Beispielprogrammen

- Zu Beginn der folgenden Beispiele ist jeweils der Ablauf der Kommunikation dargestellt.

- Die Projekte zu den nachfolgenden Quelltexten sind in folgendem .zip-File zusammengefaßt:

|

i2c_einfuehrung.zip - AVR-Studio-Projekte zu den folgenden Beispielen mit I2C-Kommunikation.

i2c_einfuehrung.zip - AVR-Studio-Projekte zu den folgenden Beispielen mit I2C-Kommunikation.

|

i2c_einfuehrung.zip - AVR-Studio-Projekte zu den folgenden Beispielen mit I2C-Kommunikation.

i2c_einfuehrung.zip - AVR-Studio-Projekte zu den folgenden Beispielen mit I2C-Kommunikation.