XADC auf dem Nexys Video

(EN google-translate)

(PL google-translate)

Nexys-Video-XADC.zip -- Digilent Beispielprojekt

Nexys-Video-XADC.zip -- Digilent Beispielprojekt

Vorgehen, um es mit VIVADO 2020.2 zum Laufen zu bekommen:

|

xadcimport3.zip -- entspricht Ordner 1 (s.o.)

xadcimport3.zip -- entspricht Ordner 1 (s.o.)

xadcimport4.zip -- entspricht Ordner 2 (s.o.)

xadcimport4.zip -- entspricht Ordner 2 (s.o.)

![Laufende Anwendung. Testanschluß: GND und H14 ---[4,7K]---J14---[4,7K]-(oder hier J14)-[33K]--- +3,3Volt. (Unterschied zwischen P-Eingang und N-Eingang darf maximal 1Volt sein.)](http://www.kramann.info/68_nexys/05_Nexys_Video/03_XADC/xadc.png)

Bild 0-1: Laufende Anwendung. Testanschluß: GND und H14 ---[4,7K]---J14---[4,7K]-(oder hier J14)-[33K]--- +3,3Volt. (Unterschied zwischen P-Eingang und N-Eingang darf maximal 1Volt sein.)

Mögliches Vorgehen ab diesem Punkt (Reengineering):

|

Einrichten eines minimalen XADC IP-Elements

Links dazu:

Vorgehen:

|

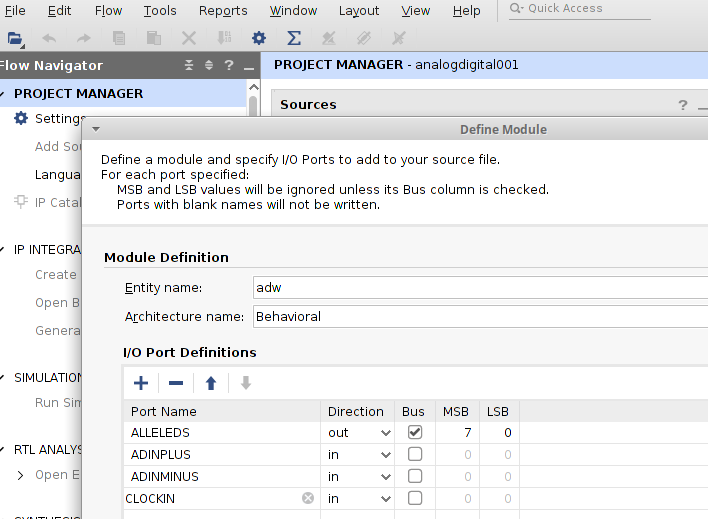

Bild 0-2: adw001.png

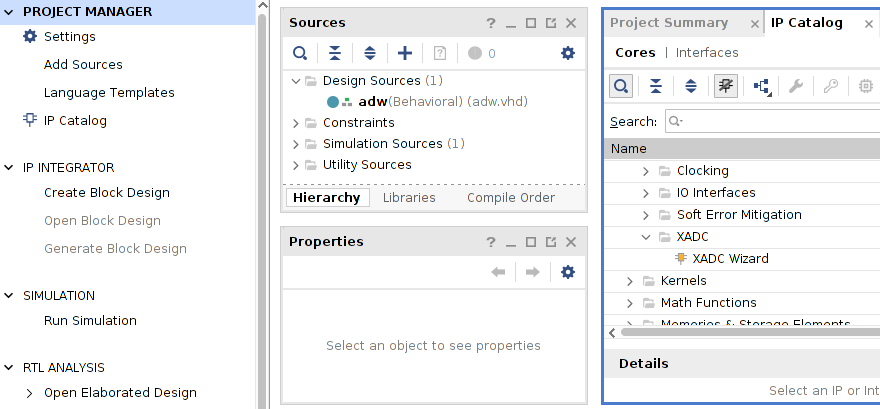

Bild 0-3: adw002_IP_catalog.png

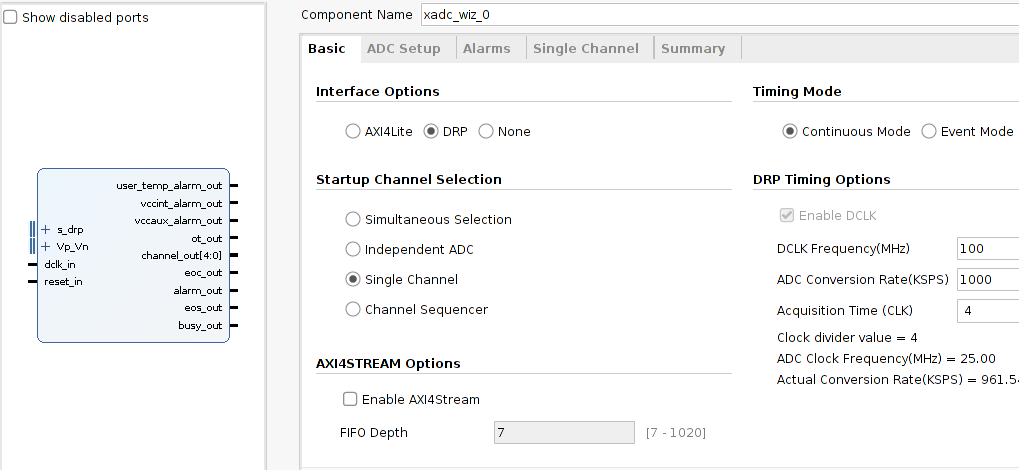

Bild 0-4: adw003_single_mode.png

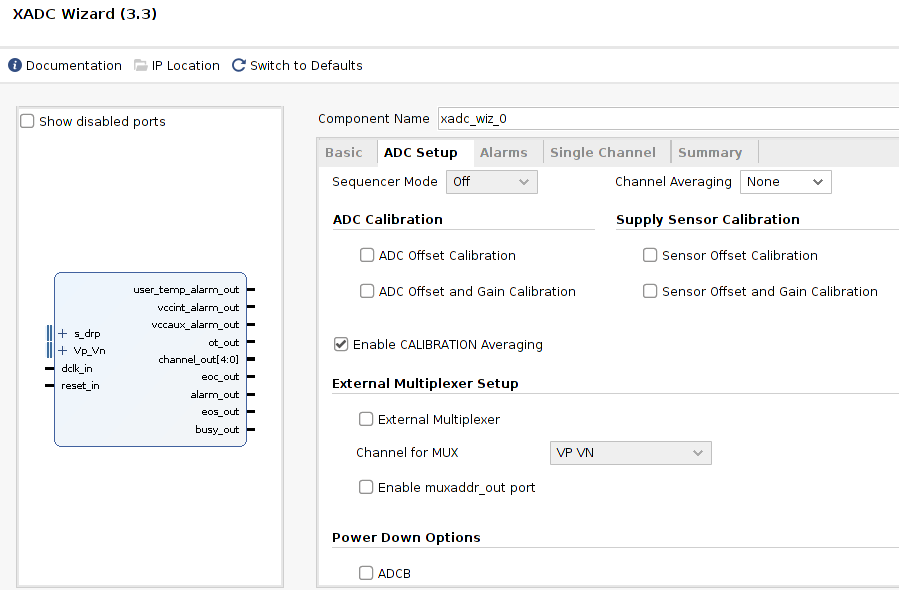

Bild 0-5: adw004_adc_setup.png

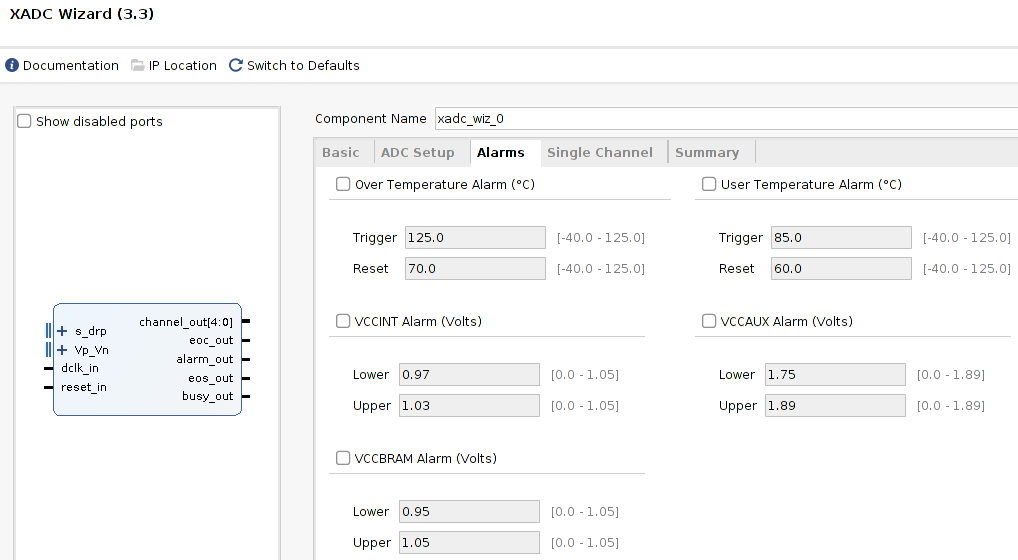

Bild 0-6: adw005_alarms_off.png

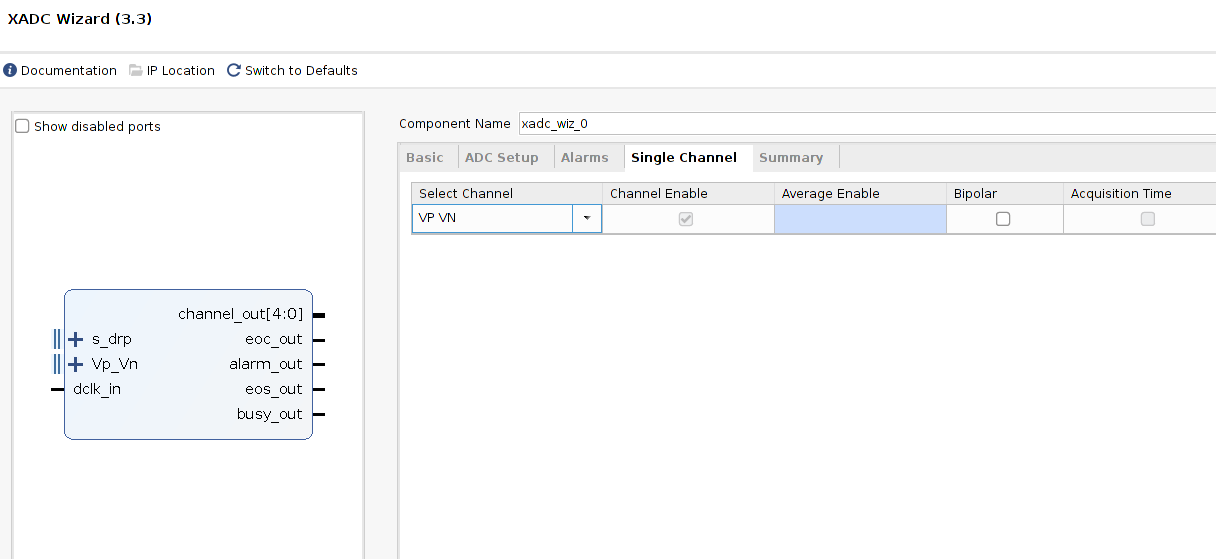

Bild 0-7: adw006b_neu_vp_vn.png

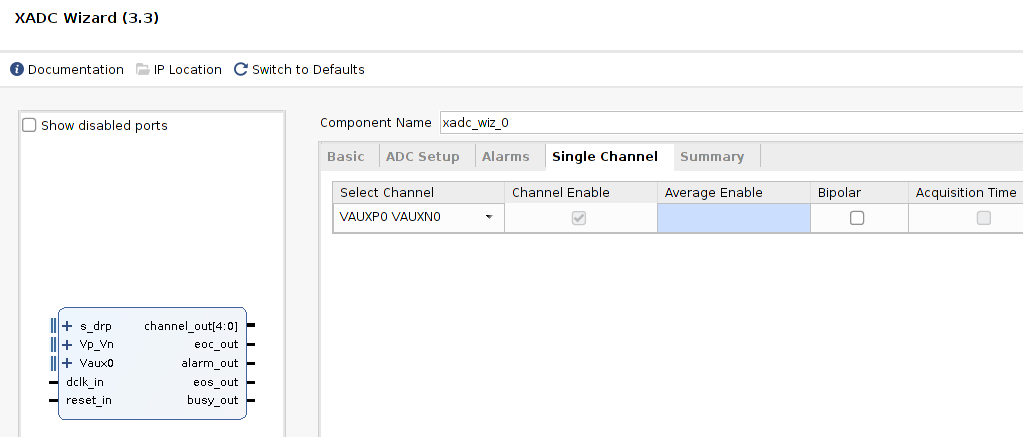

Bild 0-8: adw006_vauxp0_vauxn0.png

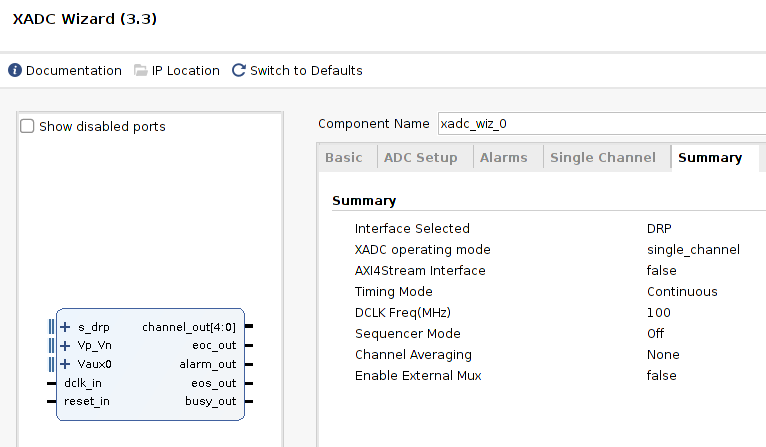

Bild 0-9: adw007_summary.png

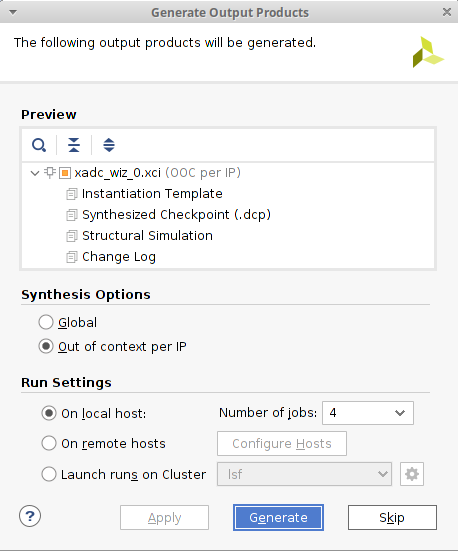

Bild 0-10: adw008_generation.png

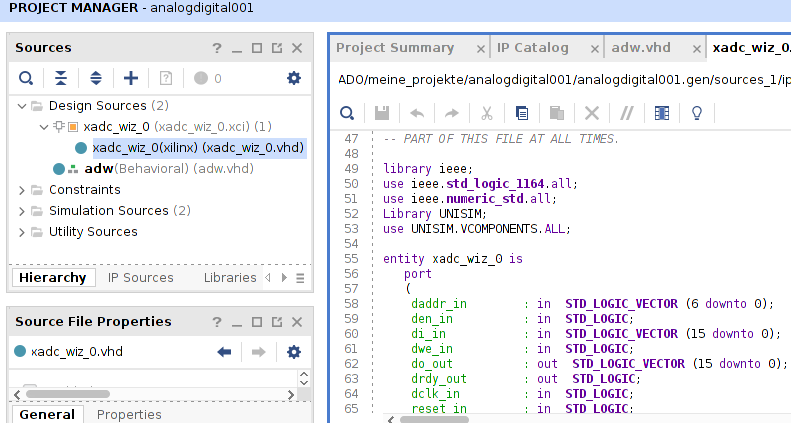

Bild 0-11: adw009_hierarchie.png

---- von vivado wizard ---

---- von vivado wizard ---

---- von vivado wizard ---

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

Library UNISIM;

use UNISIM.VCOMPONENTS.ALL;

entity xadc_wiz_0 is

port

(

daddr_in : in STD_LOGIC_VECTOR (6 downto 0) := "0000000"; -- Address bus for the dynamic reconfiguration port

den_in : in STD_LOGIC := '1'; -- Enable Signal for the dynamic reconfiguration port

di_in : in STD_LOGIC_VECTOR (15 downto 0) := "0000000000000000"; -- Input data bus for the dynamic reconfiguration port

dwe_in : in STD_LOGIC := '1'; -- Write Enable for the dynamic reconfiguration port

do_out : out STD_LOGIC_VECTOR (15 downto 0); -- Output data bus for dynamic reconfiguration port

drdy_out : out STD_LOGIC; -- Data ready signal for the dynamic reconfiguration port

dclk_in : in STD_LOGIC; -- Clock input for the dynamic reconfiguration port

busy_out : out STD_LOGIC; -- ADC Busy signal

channel_out : out STD_LOGIC_VECTOR (4 downto 0); -- Channel Selection Outputs

eoc_out : out STD_LOGIC; -- End of Conversion Signal

eos_out : out STD_LOGIC; -- End of Sequence Signal

alarm_out : out STD_LOGIC; -- OR'ed output of all the Alarms

vp_in : in STD_LOGIC; -- Dedicated Analog Input Pair

vn_in : in STD_LOGIC

);

end xadc_wiz_0;

architecture xilinx of xadc_wiz_0 is

attribute CORE_GENERATION_INFO : string;

attribute CORE_GENERATION_INFO of xilinx : architecture is "xadc_wiz_0,xadc_wiz_v3_3_8,{component_name=xadc_wiz_0,enable_axi=false,enable_axi4stream=false,dclk_frequency=100,enable_busy=true,enable_convst=false,enable_convstclk=false,enable_dclk=true,enable_drp=true,enable_eoc=true,enable_eos=true,enable_vbram_alaram=false,enable_vccddro_alaram=false,enable_Vccint_Alaram=false,enable_Vccaux_alaram=falseenable_vccpaux_alaram=false,enable_vccpint_alaram=false,ot_alaram=false,user_temp_alaram=false,timing_mode=continuous,channel_averaging=None,sequencer_mode=off,startup_channel_selection=single_channel}";

signal FLOAT_VCCAUX_ALARM : std_logic;

signal FLOAT_VCCINT_ALARM : std_logic;

signal FLOAT_USER_TEMP_ALARM : std_logic;

signal FLOAT_VBRAM_ALARM : std_logic;

signal FLOAT_MUXADDR : std_logic_vector (4 downto 0);

signal aux_channel_p : std_logic_vector (15 downto 0);

signal aux_channel_n : std_logic_vector (15 downto 0);

signal alm_int : std_logic_vector (7 downto 0);

begin

alarm_out <= alm_int(7);

aux_channel_p(0) <= '0';

aux_channel_n(0) <= '0';

aux_channel_p(1) <= '0';

aux_channel_n(1) <= '0';

aux_channel_p(2) <= '0';

aux_channel_n(2) <= '0';

aux_channel_p(3) <= '0';

aux_channel_n(3) <= '0';

aux_channel_p(4) <= '0';

aux_channel_n(4) <= '0';

aux_channel_p(5) <= '0';

aux_channel_n(5) <= '0';

aux_channel_p(6) <= '0';

aux_channel_n(6) <= '0';

aux_channel_p(7) <= '0';

aux_channel_n(7) <= '0';

aux_channel_p(8) <= '0';

aux_channel_n(8) <= '0';

aux_channel_p(9) <= '0';

aux_channel_n(9) <= '0';

aux_channel_p(10) <= '0';

aux_channel_n(10) <= '0';

aux_channel_p(11) <= '0';

aux_channel_n(11) <= '0';

aux_channel_p(12) <= '0';

aux_channel_n(12) <= '0';

aux_channel_p(13) <= '0';

aux_channel_n(13) <= '0';

aux_channel_p(14) <= '0';

aux_channel_n(14) <= '0';

aux_channel_p(15) <= '0';

aux_channel_n(15) <= '0';

U0 : XADC

generic map(

INIT_40 => X"8003", -- config reg 0

INIT_41 => X"310F", -- config reg 1

INIT_42 => X"0400", -- config reg 2

INIT_48 => X"0100", -- Sequencer channel selection

INIT_49 => X"0000", -- Sequencer channel selection

INIT_4A => X"0000", -- Sequencer Average selection

INIT_4B => X"0000", -- Sequencer Average selection

INIT_4C => X"0000", -- Sequencer Bipolar selection

INIT_4D => X"0000", -- Sequencer Bipolar selection

INIT_4E => X"0000", -- Sequencer Acq time selection

INIT_4F => X"0000", -- Sequencer Acq time selection

INIT_50 => X"B5ED", -- Temp alarm trigger

INIT_51 => X"57E4", -- Vccint upper alarm limit

INIT_52 => X"A147", -- Vccaux upper alarm limit

INIT_53 => X"CA33", -- Temp alarm OT upper

INIT_54 => X"A93A", -- Temp alarm reset

INIT_55 => X"52C6", -- Vccint lower alarm limit

INIT_56 => X"9555", -- Vccaux lower alarm limit

INIT_57 => X"AE4E", -- Temp alarm OT reset

INIT_58 => X"5999", -- Vccbram upper alarm limit

INIT_5C => X"5111", -- Vccbram lower alarm limit

SIM_DEVICE => "7SERIES",

SIM_MONITOR_FILE => "design.txt"

)

port map (

CONVST => '0',

CONVSTCLK => '0',

DADDR(6 downto 0) => daddr_in(6 downto 0),

DCLK => dclk_in,

DEN => den_in,

DI(15 downto 0) => di_in(15 downto 0),

DWE => dwe_in,

RESET => '0',

VAUXN(15 downto 0) => aux_channel_n(15 downto 0),

VAUXP(15 downto 0) => aux_channel_p(15 downto 0),

ALM => alm_int,

BUSY => busy_out,

CHANNEL(4 downto 0) => channel_out(4 downto 0),

DO(15 downto 0) => do_out(15 downto 0),

DRDY => drdy_out,

EOC => eoc_out,

EOS => eos_out,

JTAGBUSY => open,

JTAGLOCKED => open,

JTAGMODIFIED => open,

OT => open,

MUXADDR => FLOAT_MUXADDR,

VN => vn_in,

VP => vp_in

);

end xilinx;

---- ENDE von vivado wizard ----

---- ENDE von vivado wizard ----

---- ENDE von vivado wizard ----

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity adw is

Port ( ALLELEDS : out STD_LOGIC_VECTOR (7 downto 0) := "00000000";

ADINPUTP : in STD_LOGIC;

ADINPUTN : in STD_LOGIC;

MEINECLOCK : in STD_LOGIC);

end adw;

architecture Behavioral of adw is

signal AUSGANG : std_logic_vector (15 downto 0) := "0000000000000000";

signal READY : STD_LOGIC := '0';

begin

process begin

wait until rising_edge(READY);

ALLELEDS <= AUSGANG(15 downto 8);

end process;

MEINADW: entity work.xadc_wiz_0

port map(

vp_in => ADINPUTP,

vn_in => ADINPUTN,

-- vauxp0 => ADINPUTP,

-- vauxn0 => ADINPUTN,

do_out => AUSGANG,

dclk_in => MEINECLOCK,

drdy_out => READY);

--ALLELEDS <= AUSGANG(15 downto 8);

end Behavioral;

Code 0-1: Beispiel-Quelltext (Nicht lauffähig!)

nexysadw004.zip -- zugehöriges VIVADO-Projekt.

nexysadw004.zip -- zugehöriges VIVADO-Projekt.