Erste Testprojekte mit dem Nexys-Video unter Verwendung der vorhandenen LEDs, Taster und Schalter

(EN google-translate)

(PL google-translate)

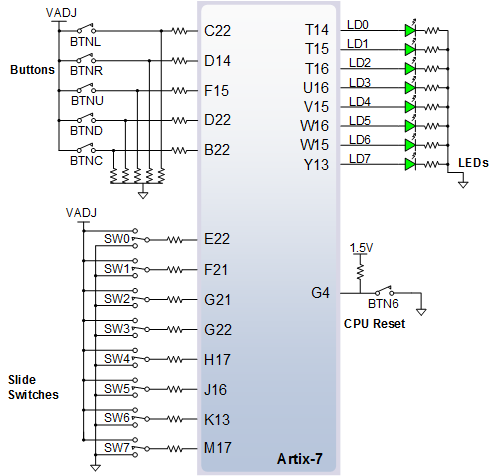

Die Pinbelegungen aller nachfolgenden Beispiele kann aus dem folgenden Schaubild zu den Tastern, Schaltern und LEDs und der zugehörigen Port-Namen auf dem FPGA entnommen werden:

Bild 0-1: Pinbelegungen für bereits auf dem Board verschaltete digitale I/Os. Quelle: Digilent.

Bild 0-2: Angaben zur Belastbarkeit der Pins (Strom). Quelle: Xilinx, ds181_Artix_7_Data_Sheet.pdf Seite 2.

Bild 0-3: Angaben zur Belastbarkeit der Pins (Spannung). Quelle: Xilinx, ds181_Artix_7_Data_Sheet.pdf Seite 2.

Bild 0-4: Spezifikation des FPGAs bei ISE 14.7

|

Bild 0-5: Bedeutung des FPGA-Namens. Quelle: Xilinx ds180_7Series_Overview.pdf Seite 16.

Vorprojekt: LED bei T14 einschalten

Siehe auch die ISE14.7-basierte Anleitung hier: 68_nexys/01_Installation/03_ISE14neu

Siehe auch die ISE14.7-basierte Anleitung hier: 68_nexys/01_Installation/03_ISE14neu

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity led is

Port ( ausgang : out STD_LOGIC);

end led;

architecture Behavioral of led is

begin

ausgang <= '1';

end Behavioral;

Code 0-1: VHDL-Code LED einschalten.

NET "ausgang" LOC = "T14"; NET "ausgang" IOSTANDARD = LVCMOS33;

Code 0-2: Constraints mit ISE 14.7 zu LED einschalten.

led.zip -- VIVADO 2020.2 Projekt für LED einschalten.

led.zip -- VIVADO 2020.2 Projekt für LED einschalten.

Um erste Tests mit dem Board vorzunehmen, werden zwei kleine Projekte in VHDL ausgeführt: Mustervergleich und Blinkled. Beide Projekte wurden bereits im Kurs FPGA eingeführt und auf den DLP-FPGA von Digikey gebracht (Spartan 3-Architektur). Hier werden sie lediglich an den Artix 7 und das Nexys-Video-Board angepaßt.

69_FPGA/05_Beispiele/01_Blinkende_LED -- Ursprüngliches Projekte blinkled.

69_FPGA/05_Beispiele/01_Blinkende_LED -- Ursprüngliches Projekte blinkled.

69_FPGA/05_Beispiele/03_Mustervergleich -- Ursprüngliches Projekt mustervergleich.

69_FPGA/05_Beispiele/03_Mustervergleich -- Ursprüngliches Projekt mustervergleich.

mustervergleich

Video: Mit Vivado ein VHDL-Projekt mustervergleich erstellen und auf den nexys video übertragen

vivado_vhdl_proj_nexys_teil_1.mp4

vivado_vhdl_proj_nexys_teil_1.mp4

vivado_vhdl_proj_nexys_teil_2.mp4

vivado_vhdl_proj_nexys_teil_2.mp4

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity mustervergleich is

Port ( A1 : in STD_LOGIC;

A0 : in STD_LOGIC;

B1 : in STD_LOGIC;

B0 : in STD_LOGIC;

C : out STD_LOGIC);

end mustervergleich;

architecture Behavioral of mustervergleich is

begin

C <= (A1 xnor B1) and (A0 xnor B0);

end Behavioral;

Code 0-3: VHDL-Quelltext für mustervergleich für den Artix 7.

## FPGA Configuration I/O Options

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property CFGBVS VCCO [current_design]

## Slide Switches

set_property -dict {PACKAGE_PIN E22 IOSTANDARD LVCMOS12} [get_ports {A1}];

set_property -dict {PACKAGE_PIN F21 IOSTANDARD LVCMOS12} [get_ports {A0}];

set_property -dict {PACKAGE_PIN G21 IOSTANDARD LVCMOS12} [get_ports {B1}];

set_property -dict {PACKAGE_PIN G22 IOSTANDARD LVCMOS12} [get_ports {B0}];

## LEDs

set_property -dict {PACKAGE_PIN T14 IOSTANDARD LVCMOS25} [get_ports {C}];

Code 0-4: Constraints mit VIVADO, .xdc-Datei.

NET "A1" LOC = "E22" | PULLUP | IOSTANDARD = LVCMOS33 ; NET "A0" LOC = "F21" | PULLUP | IOSTANDARD = LVCMOS33 ; NET "B1" LOC = "G21" | PULLUP | IOSTANDARD = LVCMOS33 ; NET "B0" LOC = "G22" | PULLUP | IOSTANDARD = LVCMOS33 ; NET "C" LOC = "T14" | IOSTANDARD = LVCMOS33 | SLEW = SLOW ;

Code 0-5: Constraints mit ISE 14.7, .ucf-Datei (gleiche Funktion wie .xdc-Datei).

nexybitvergleich2.zip -- VIVADO 2020.2 Projekt zu mustervergleich für Artix 7.

nexybitvergleich2.zip -- VIVADO 2020.2 Projekt zu mustervergleich für Artix 7.

nexysvideomustervergleich.zip -- ISE 14.7 Projekt zu mustervergleich für Artix 7.

nexysvideomustervergleich.zip -- ISE 14.7 Projekt zu mustervergleich für Artix 7.

blinkled

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity blinkled is

Port ( MEINECLOCK : in STD_LOGIC;

MEINELED : out STD_LOGIC);

end blinkled;

-- Clock-In == 100MHz, Toggeln nach 50000000 Schritten ergibt 1Hz Blinkfrequenz.

architecture Behavioral of blinkled is

signal zaehler : integer range 0 to 49999999 := 0;

signal logikpegel : std_logic := '0';

begin

process begin

wait until rising_edge(MEINECLOCK);

if (zaehler<49999999) then

zaehler <= zaehler+1;

else

zaehler <= 0;

logikpegel <= not logikpegel;

end if;

end process;

MEINELED <= logikpegel;

end Behavioral;

Code 0-6: VHDL-Datei zu blinkled auf Artix 7. (100MHz-Takt auf 1Hz Blinken herunter geteilt.)

## GCLK6 ist auf FPGA-Chip Pin 56 NET "MEINECLOCK" LOC = "R4"; ## IO_L05P_0 ist auf FPGA-Chip Pin 125 NET "MEINELED" LOC = "T14"; NET "MEINECLOCK" IOSTANDARD = LVCMOS25; NET "MEINELED" IOSTANDARD = LVCMOS33;

Code 0-7: Constraints mit ISE 14.7 für blinkled, .ucf-Datei (gleiche Funktion wie .xdc-Datei).

nexysvideoblinkled.zip -- ISE 14.7 Projekt zu blinkled (1Hz) für Artix 7.

nexysvideoblinkled.zip -- ISE 14.7 Projekt zu blinkled (1Hz) für Artix 7.