Die PMOD-Schnittstellen auf dem Nexys Video

(EN google-translate)

(PL google-translate)

|

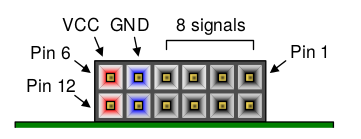

Bild 0-1: Pinbelegung der PMOD-Anschlüsse auf dem Board. Quelle: Digilent, FPGA-Board Reference Manual.

|

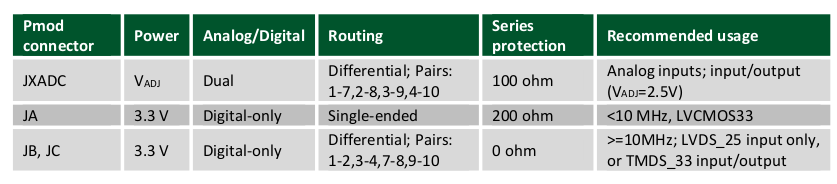

Bild 0-2: Anwendungsmöglichkeiten der vier PMOD-Anschlüsse. Quelle: Digilent, FPGA-Board Reference Manual.

|

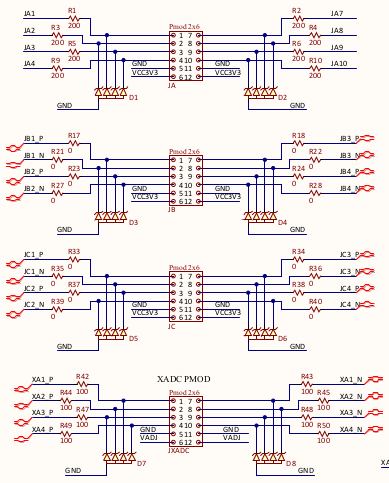

Bild 0-3: Verschaltung der PMOD-Schnittstellen auf dem Board. Quelle: Digilent, FPGA-Board Verschaltung.

|

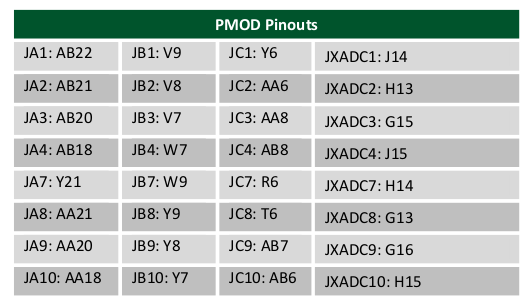

Bild 0-4: Bezeichner der PMOD-Pins für die Programmierung. Quelle: Digilent, FPGA-Board Reference Manual.

Experiment 1: Blinkende LED an PMOD JA, Pin4 (in VHDL: AB18) gegen Ground (Pin 5)

Das Projekt unterscheidet sich minimal von dem voran umgesetzten Projekt blinkled. Lediglich der Ausgang muß in den Constraints von T14 auf AB18 umgesetzt werden. Außerdem wird die Spannung mit LVCMOS12 auf 1,2 Volt gesetzt. Damit liegt die Last maximal bei 6mA (vergl. weiter oben):

blinkled

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity blinkled is

Port ( MEINECLOCK : in STD_LOGIC;

MEINELED : out STD_LOGIC);

end blinkled;

-- Clock-In == 100MHz, Toggeln nach 50000000 Schritten ergibt 1Hz Blinkfrequenz.

architecture Behavioral of blinkled is

signal zaehler : integer range 0 to 49999999 := 0;

signal logikpegel : std_logic := '0';

begin

process begin

wait until rising_edge(MEINECLOCK);

if (zaehler<49999999) then

zaehler <= zaehler+1;

else

zaehler <= 0;

logikpegel <= not logikpegel;

end if;

end process;

MEINELED <= logikpegel;

end Behavioral;

Code 0-1: VHDL-Datei zu blinkled auf Artix 7. (100MHz-Takt auf 1Hz Blinken herunter geteilt.)

## GCLK6 ist auf FPGA-Chip Pin 56 NET "MEINECLOCK" LOC = "R4"; ## IO_L05P_0 ist auf FPGA-Chip Pin 125 NET "MEINELED" LOC = "AB18"; NET "MEINECLOCK" IOSTANDARD = LVCMOS25; NET "MEINELED" IOSTANDARD = LVCMOS12;

Code 0-2: Constraints mit ISE 14.7 für blinkled, .ucf-Datei (gleiche Funktion wie .xdc-Datei).

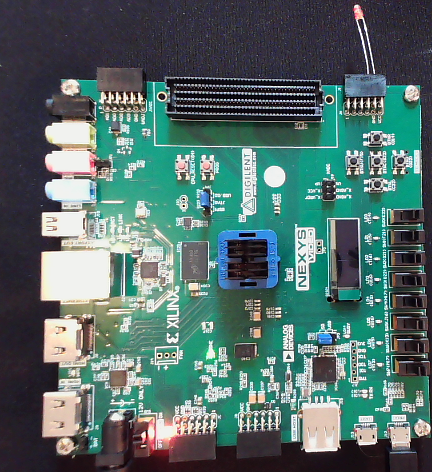

Bild 0-5: 3mm LED bei JA, Pin 4 (AB18, langes Beinchen) und Pin 5 (GND, kurzes Beinchen).

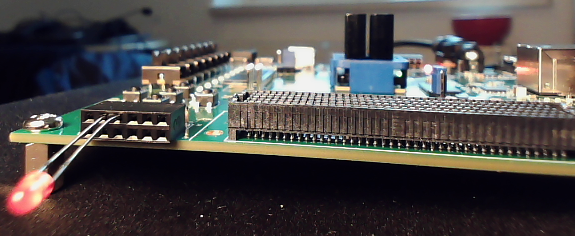

Bild 0-6: Nahansicht, 3mm LED bei JA, Pin 4 (AB18, langes Beinchen) und Pin 5 (GND, kurzes Beinchen).

nexysvideoblinkled.zip -- modifiziertes ISE 14.7 Projekt blinkled.

nexysvideoblinkled.zip -- modifiziertes ISE 14.7 Projekt blinkled.